时间:2023-07-04 15:17

人气:

作者:admin

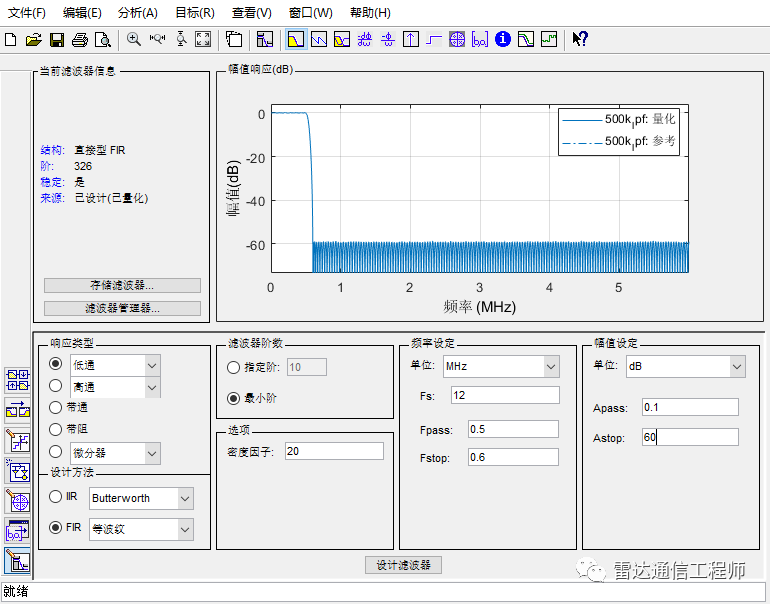

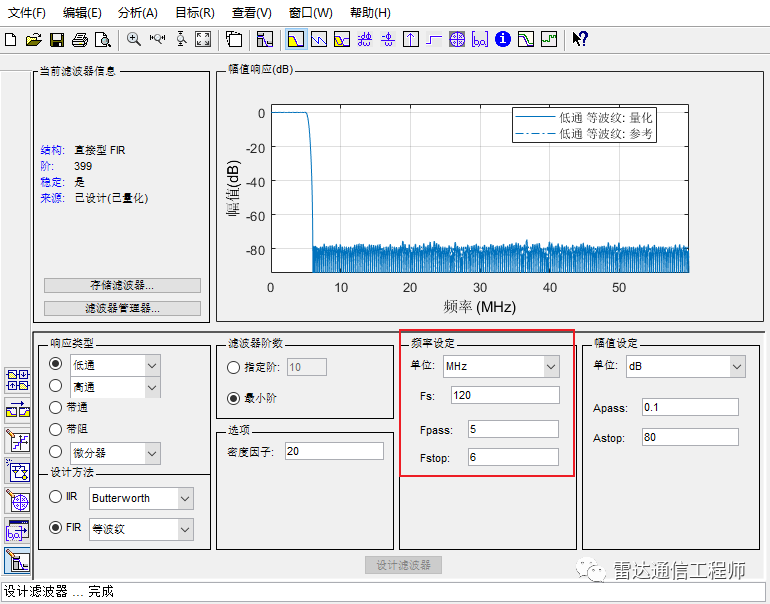

前段时间用matlab仿真了一波基于FFT卷积的频域FIR滤波器,比如采样率12MHz,需要做一个如下图所示的500KHz低通滤波器(带外抑制仅60dBc),滤波器的阶数为326阶,以XC7K325T的DSP资源数约840作为参考,在12MHz的时钟下只能实现5个这样的滤波器,在采用高频时钟后可以减低DSP资源使用率,但是当归一化频率不变,采样率上升到120MHz,同样的系数滤波器的低通截止频率为5MHz,虽然系数不变,但此时将很难再大幅提高时钟频率复用资源来降低占用率了,一方面不同规格的FPGA芯片都有其自身的频率限制,另一方面逻辑设计本身也会存在时许限制。

带外抑制60dbc的阶数=326

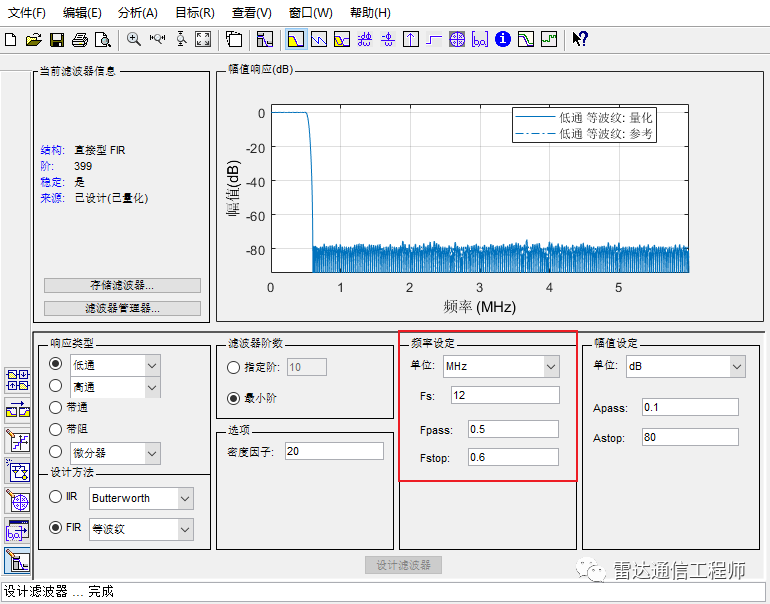

带外抑制80dBc的阶数=399

归一化频率不变,采样率提升到120MHz时(注意:滤波器系数是相同的)

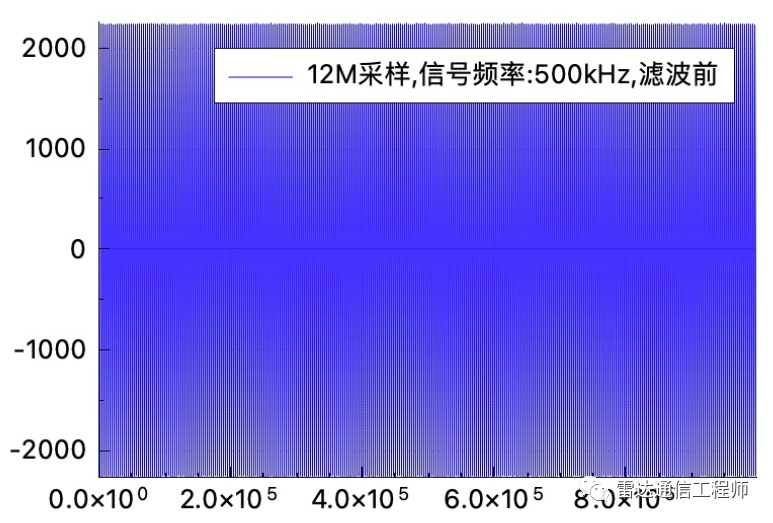

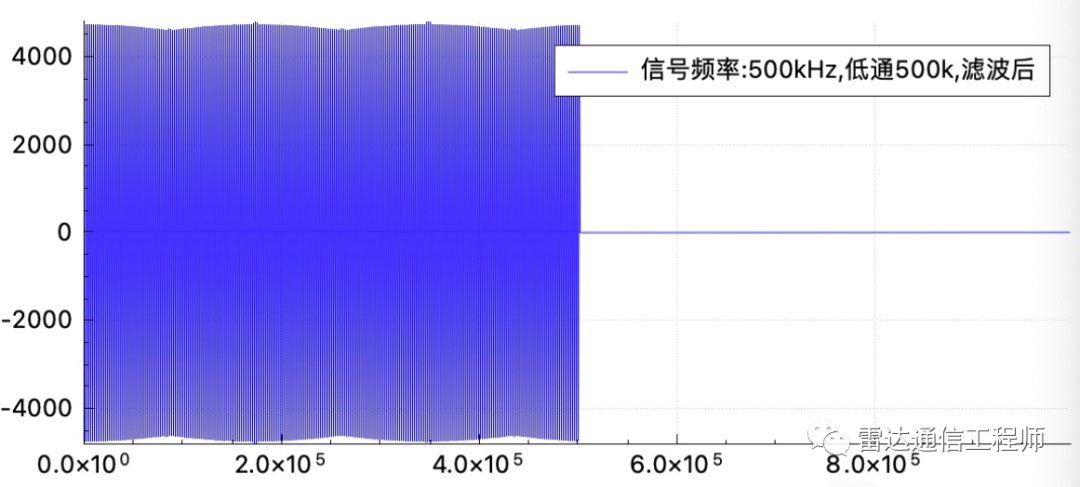

以下为FFT卷积算法在Qt的C\\C++环境下的实现FIR滤波的效果

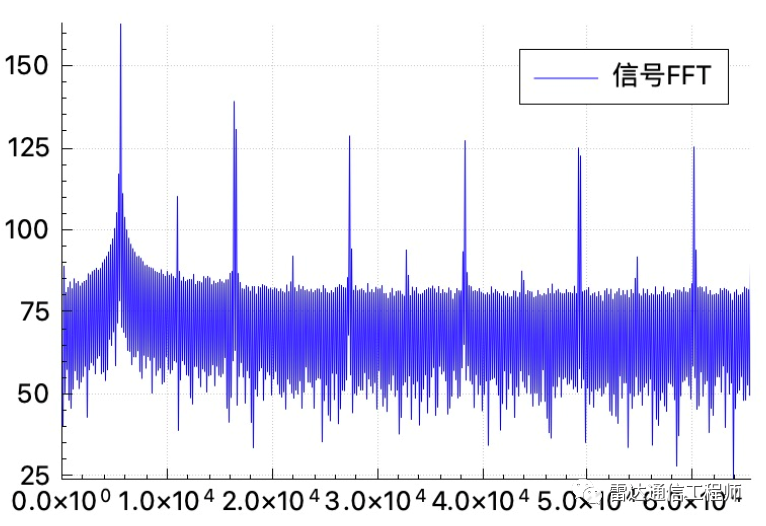

原始信号的FFT结果即为常见的信号频谱,该信号存在较强的高次谐波

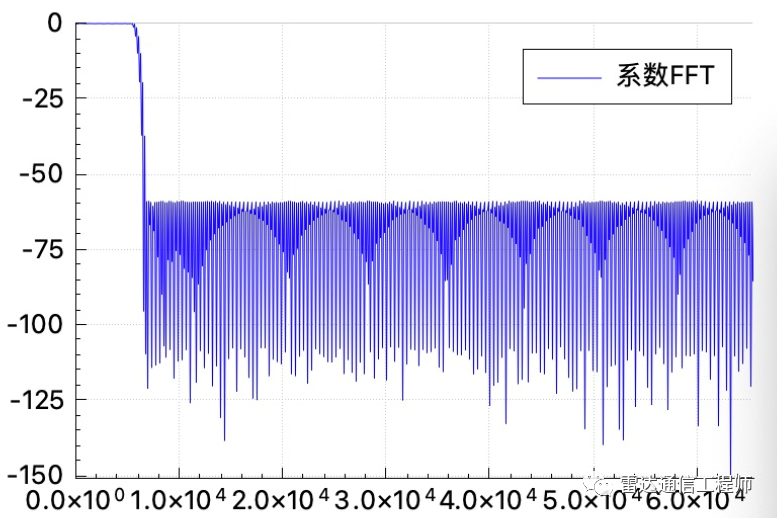

而滤波器系数FFT后得到的是滤波器的幅频特性曲线,这一点比较有意思,滤波器系数实际是该滤波器的时域冲击响应波形的离散采样

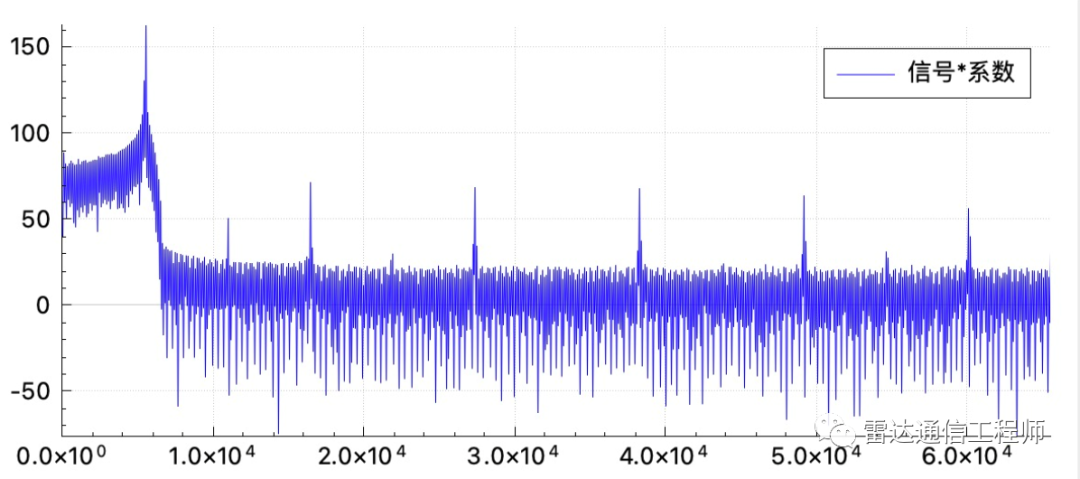

以上为滤波后的频域结果,图中500Khz以外的频谱部分全部被抑制了大约60dBc;

下一篇:定时器在编程中有什么作用

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有