时间:2023-05-25 15:06

人气:

作者:admin

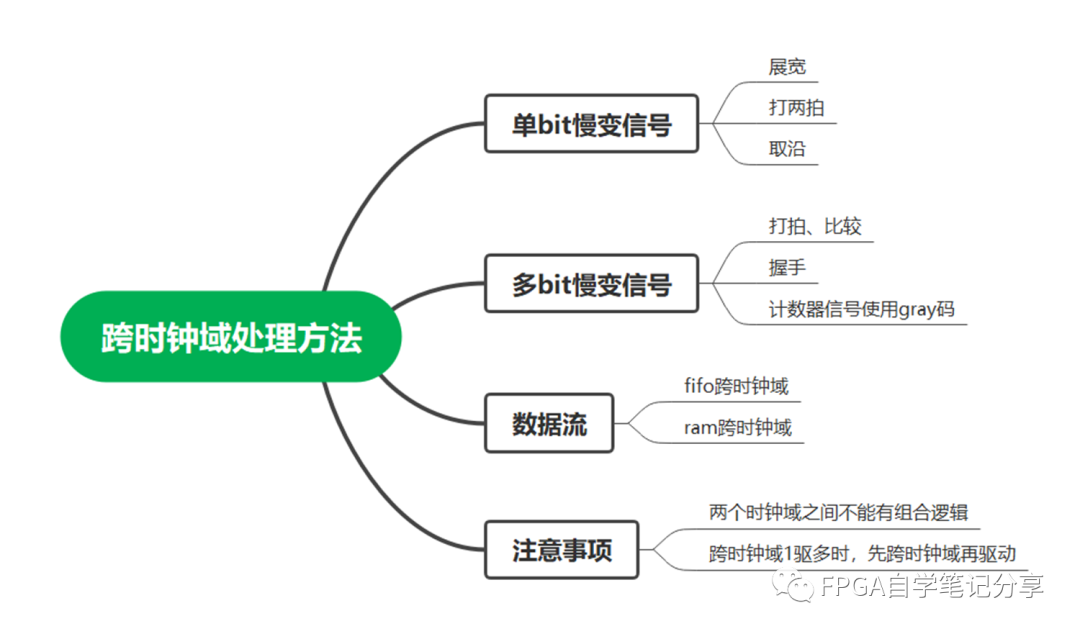

跨时钟域是FPGA设计中最容易出错的设计模块,而且一旦跨时钟域出现问题,定位排查会非常困难,因为跨时钟域问题一般是偶现的,而且除非是构造特殊用例一般的仿真是发现不了这类问题的。

优秀的FPGA工程,系统工程师一定会进行合理的时钟域划分,理想的情况是整个工程只有一个时钟,完全不考虑跨时钟域的问题,但是实际的工程中一般是不存在的,因此合理的跨时钟域设计是很有必要的。

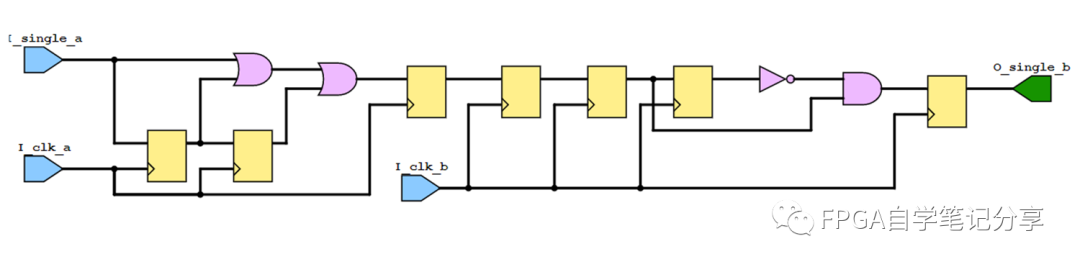

单bit慢变信号跨时钟域方法:

1、信号展宽

2、跨时钟打两拍

3、取沿

// ============================================================

// File Name: cm_cdc_1bit

// VERSION : V1.0

// DATA : 2022/9/28

// Author : FPGA干货分享

// ============================================================

// 功能:单bit慢变信号跨时钟域模块

// ============================================================

`timescale 1ns/1ps

module cm_cdc_1bit (

input wire I_clk_a , ///输入时钟a

input wire I_clk_b , ///输入时钟b

input wire I_single_a , ///a时钟输入信号

output reg O_single_b ///b时钟输出信号

);

// ============================================================

// wire reg

// ============================================================

reg S_clr_flag_a_d0 ;

reg S_clr_flag_a_d1 ;

reg S_clr_flag_a_all ;

reg S_clr_flag_b_d0 ;

reg S_clr_flag_b_d1 ;

reg S_clr_flag_b_d2 ;

reg S_clr_b_posedge ;

// ============================================================

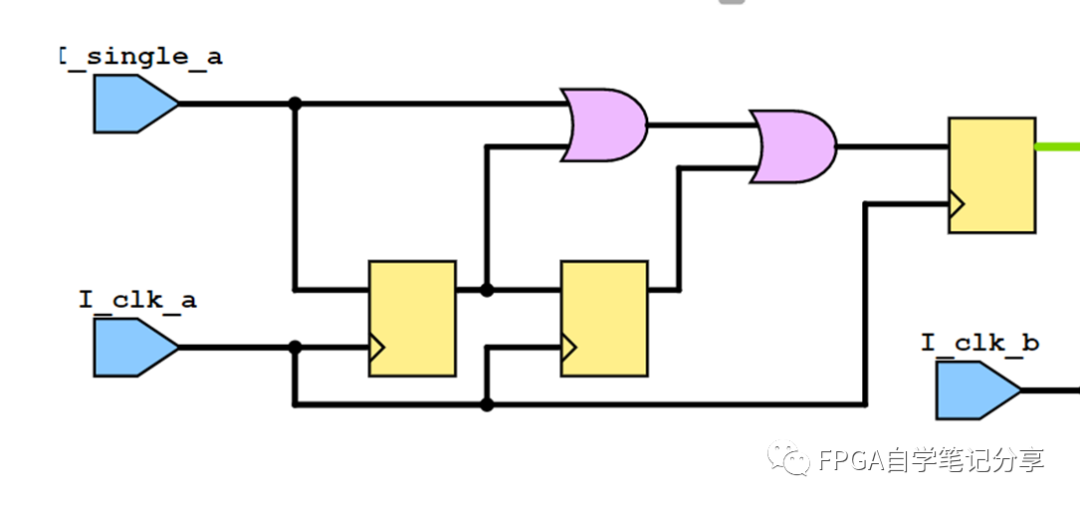

// a时钟域

// ============================================================

always @(posedge I_clk_a)

begin

S_clr_flag_a_d0 <= I_single_a;

S_clr_flag_a_d1 <= S_clr_flag_a_d0;

end

///跨时钟域之前先扩展

always @(posedge I_clk_a)

S_clr_flag_a_all <= I_single_a|S_clr_flag_a_d0|S_clr_flag_a_d1 ;

// ============================================================

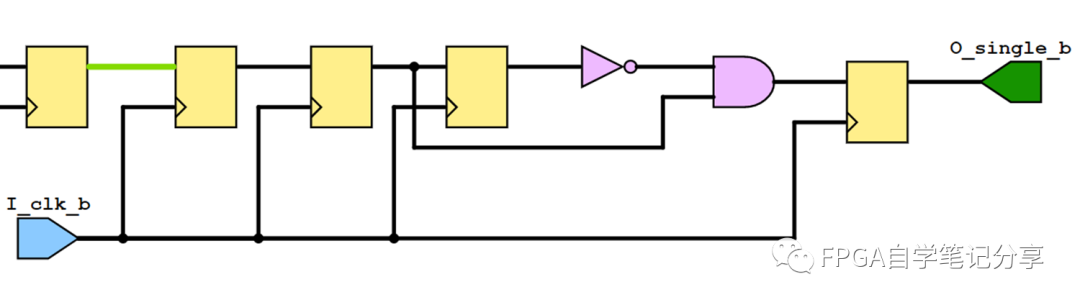

// b时钟域

// ============================================================

///使用第二个时钟进行打拍

always @(posedge I_clk_b)

begin

S_clr_flag_b_d0 <= S_clr_flag_a_all;

S_clr_flag_b_d1 <= S_clr_flag_b_d0 ;

S_clr_flag_b_d2 <= S_clr_flag_b_d1 ;

end

//打两拍之后的信号进行处理

always @(posedge I_clk_b)

O_single_b <= (!S_clr_flag_b_d2)&(S_clr_flag_b_d1);

endmodule

上一篇:FPGA设计中如何防止信号被优化

下一篇:FPGA跨时钟域处理方法(二)

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有