时间:2023-05-25 15:22

人气:

作者:admin

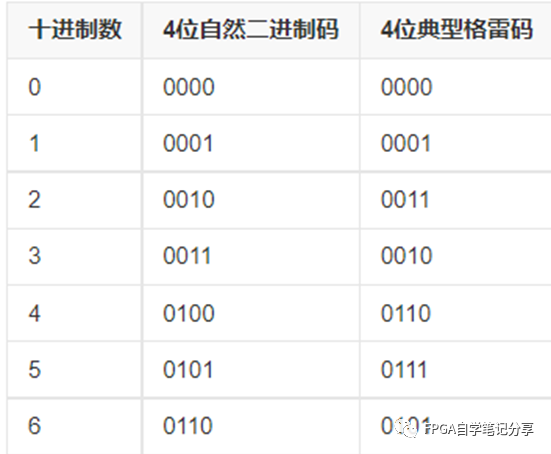

上一篇文章我们讲了二进制转gray码,这次我们聊一下gray码转二进制码。

格雷码解码:

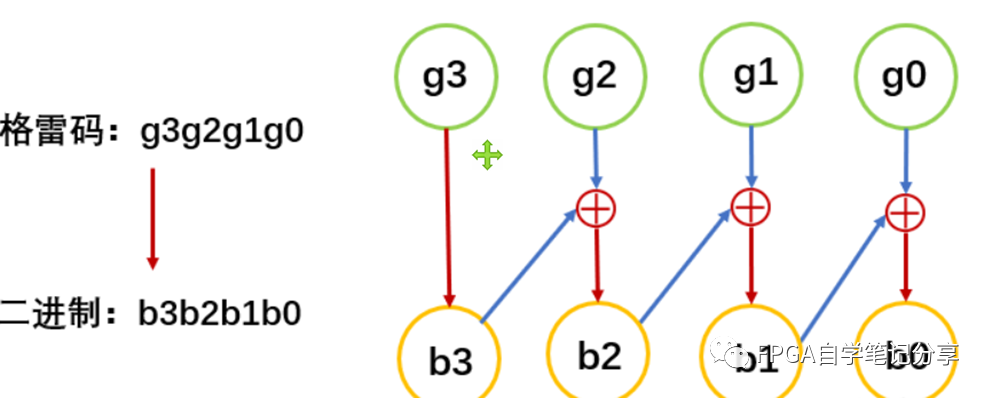

原码:b[0~n]; 格雷码:g0~n; 解码:b=F(g);

??:b[n]=g[n],b=g XOR bI+1.

代码如下:

//============================================================

// File Name: cm_gray2bin

// VERSION : V1.0

// DATA : 2022/10/2

// Author : FPGA干货分享

// ============================================================

// 功能:二级制编码转格雷码

//

// 原码:b[0~n];格雷码:g[0~n](n∈N);编码:g=G(b);解码:b=F(g);

// 编码:g=b XOR b[i+1](i∈N,0≤i≤n-1),g[n]=b[n];

// 解码:b[n]=g[n],b=g XOR b[i+1](i∈N,0≤i≤n-1).

//

// ============================================================

`timescale 1ns/1ps

module cm_gray2bin #(

parameter C_DATA_WIDTH = 4 )

(

input wire I_sys_clk , ///输入时钟

input wire [C_DATA_WIDTH-1:0] I_data_gray , ///输入gray码

output reg [C_DATA_WIDTH-1:0] O_data_bin ///输出二进制数据

);

// ============================================================

// wire reg

// ============================================================

wire [C_DATA_WIDTH-1:0] S_data_bin ;

// ============================================================

// main code

// ============================================================

assign S_data_bin[C_DATA_WIDTH-1] = I_data_gray[C_DATA_WIDTH-1];

assign S_data_bin[C_DATA_WIDTH-2:0] = I_data_gray[C_DATA_WIDTH-2:0]^S_data_bin[C_DATA_WIDTH-1:1];

always @(posedge I_sys_clk)

O_data_bin <= S_data_bin;

endmodule

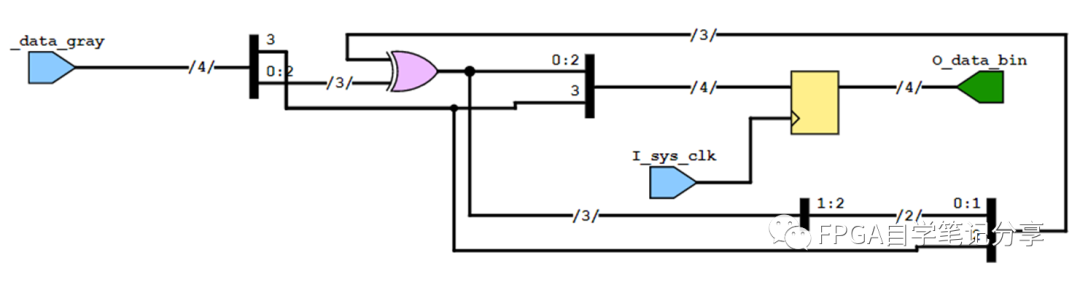

代码综合结果如下:

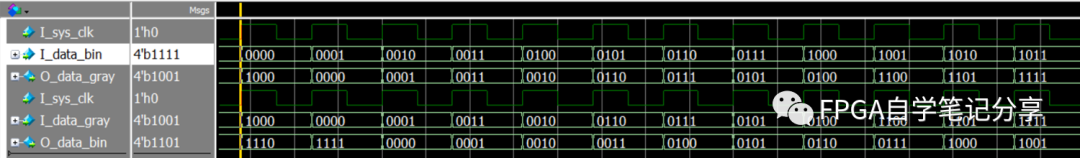

仿真如下:

下一篇:什么是VC02虚拟元器件仿真器

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有