时间:2023-03-24 15:56

人气:

作者:admin

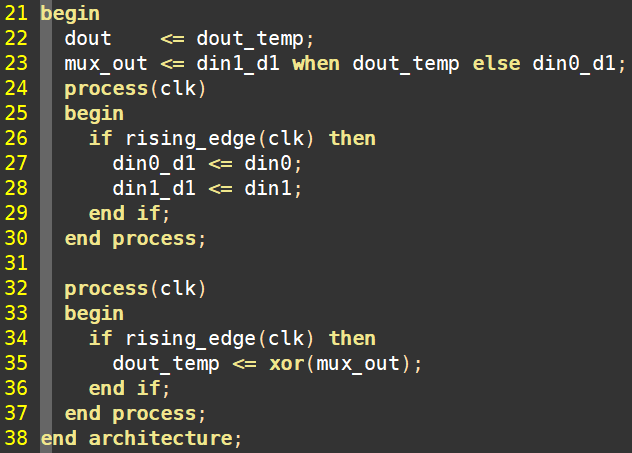

在FPGA设计中,我们可能会碰到这样的路径,如下图所示。图中两个输入数据为64位,寄存一拍后给到二选一MUX的数据输入端,MUX的输出数据经位缩减运算经输出寄存器输出,而输出寄存器的输出又反馈回来作为MUX的控制端,如图中蓝色标记所示。

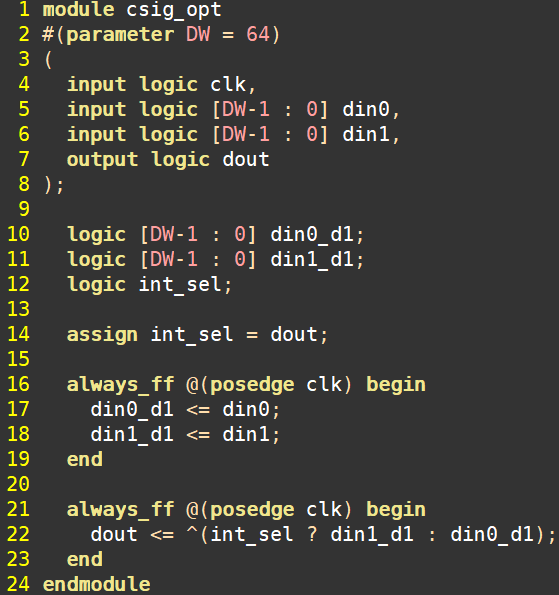

相应的SystemVerilog代码如下图所示:

相应的VHDL代码如下:

从布线后的结果来看,反馈路径成为关键路径,这可通过布线后的结果回溯到RTL视图,如下图所示。注意到图中触发器的扇出为33。

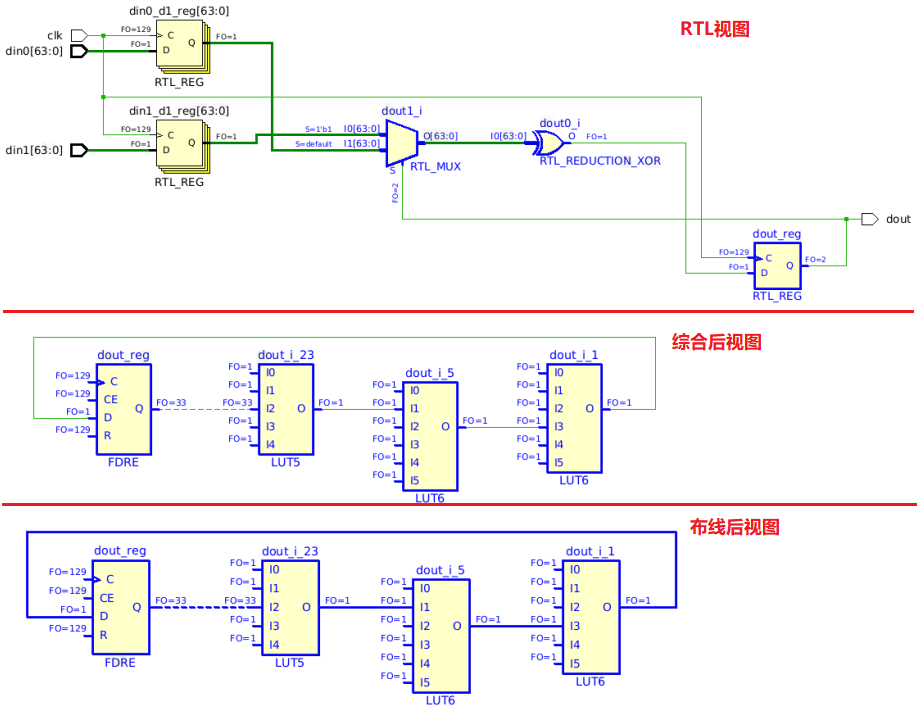

对于此类反馈路径,我们可以采用综合属性CRITICAL_SIG_OPT进行优化(该综合属性只可以在Vivado 2022.2及其之后的版本中使用)。将其施加在dout上,如下图所示。

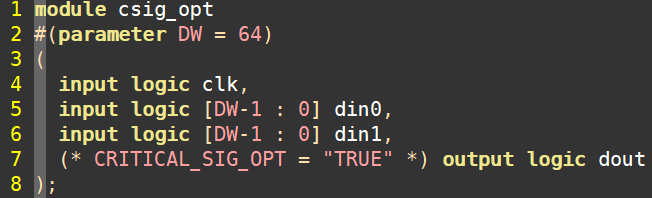

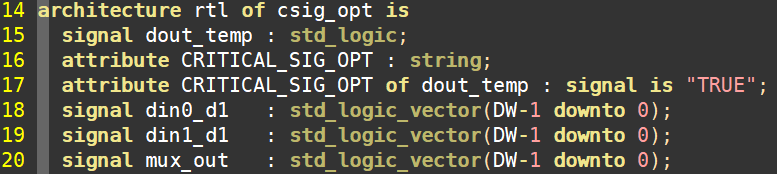

如果是VHDL代码,应采用如下方式使用CRITICAL_SIG_OPT:

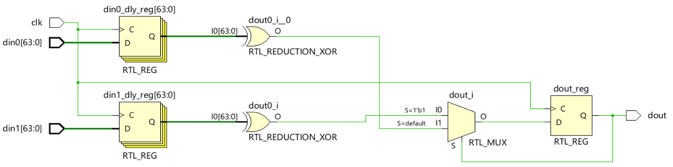

这个综合属性会将位缩减运算前移,这样二选一MUX的输入数据就变为1位,如下图所示,这正是我们所期望的。

从布线后的视图回溯到综合后以及RTL视图,如下图所示。此时关键路径发生了变化,从输入端经二选一MUX过位缩减运算器到末级输出触发器,不再是原来的反馈之路。而末级输出触发器的扇出也降低到2。

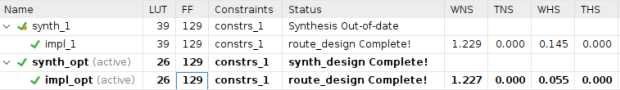

再从资源利用率角度看,优化前使用了39个LUT,129个FF,而优化后使用了26个LUT,129个FF,LUT个数降低了,FF个数保持不变,如下图所示。

综合属性CRITICAL_SIG_OPT从Vivado 2022.2版本开始支持,适用于优化反馈路径,可有效缓解反馈路径的时序压力。

审核编辑:刘清

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有