时间:2021-01-25 09:52

人气:

作者:admin

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

实验Vivado工程为“lcd7_test”。

基于HDMI输出实验,本章介绍7寸液晶屏的显示。

7寸LCD触摸屏模块是由TFT 液晶屏,电容触摸屏和驱动板组成,实物照片如下:

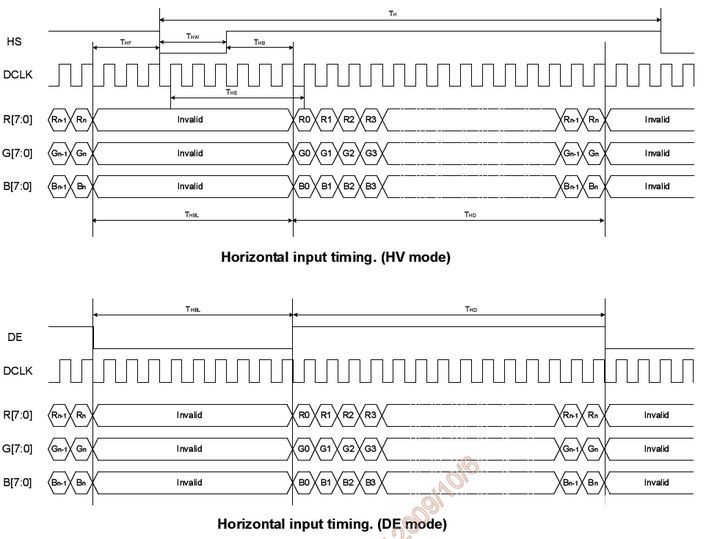

LCD屏显示方式从屏幕左上角一点开始,从左向右逐点显示,每显示完一行,再回到屏幕的左边下一行的起始位置,在这期间,需要对行进行消隐,每行结束时,用行同步信号进行同步;LCD的驱动有两种方式,一种为HV模式,另一种为DE模式,这两种模式都能驱动LCD屏,数据在DCLK的上升沿采样。以下为行显示的时序图:

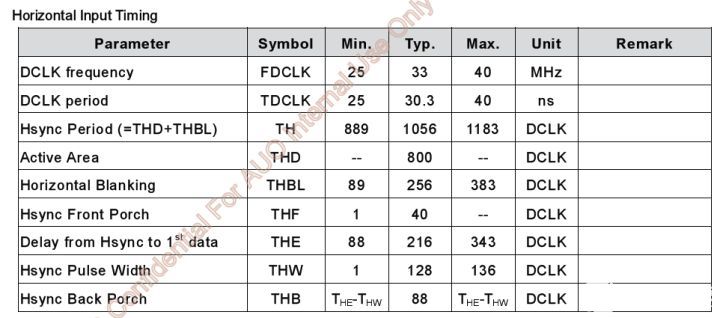

LCD行的显示时序参数如下表所示:

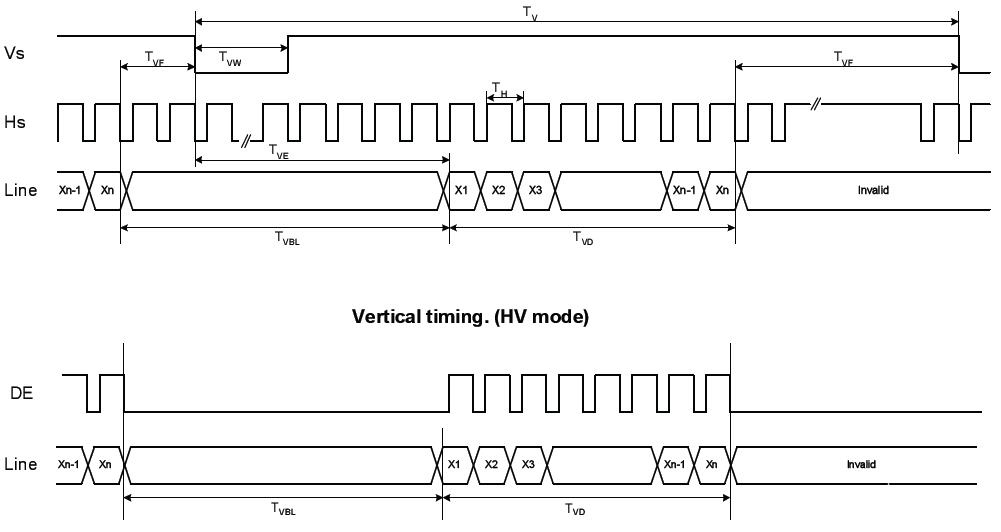

当显示完所有的行,形成一帧,用场同步信号进行场同步,并使LCD显示回到屏幕左上方,同时进行场消隐,开始下一帧。以下为列显示的时序图:

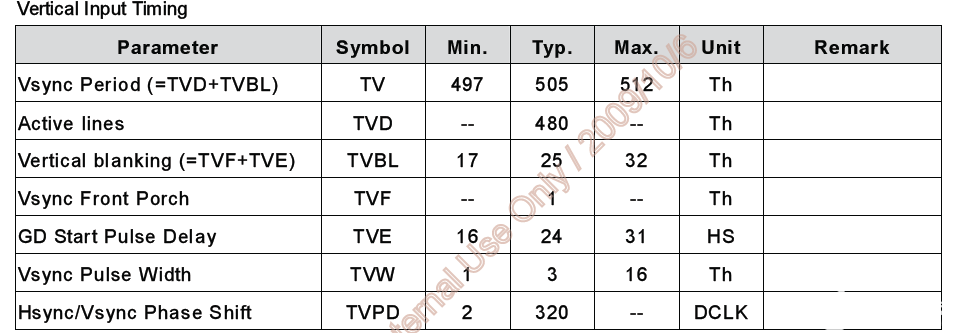

LCD列的显示时序参数如下表所示:

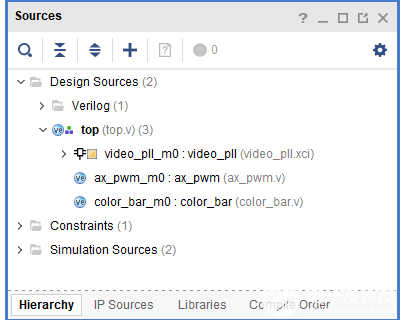

本章实验其实很简单,与HDMI显示最大的不同是不需要i2c配置,输出按照RGB即可。以下是文件结构。

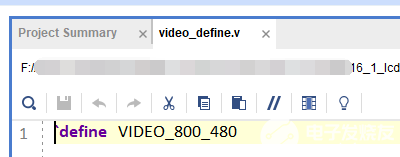

同时因为液晶屏的分辨率是800x480,需要修改video_define.v的宏定义。

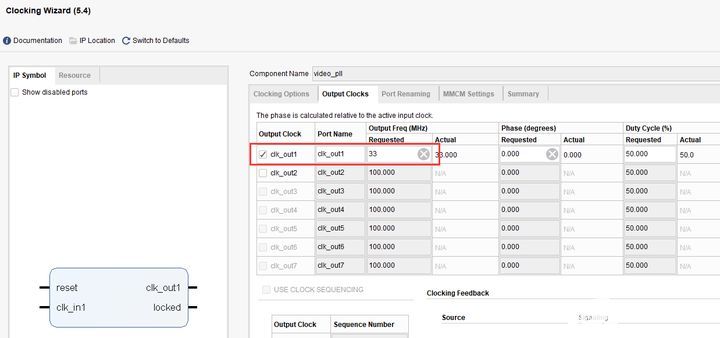

同时将PLL的输出时钟频率修改为33MHz,即800x480的像素时钟。

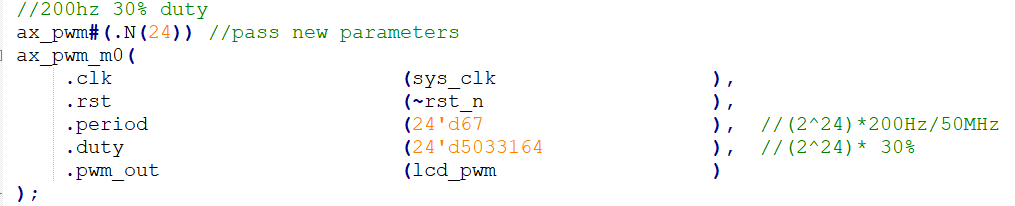

同时在top.v中例化了ax_pwm,用于调节液晶屏的亮度,设置为200Hz,30%点空比。

连接液晶屏到J15扩展口,下载程序,即可看到彩条显示。

同时也准备了字符显示的例程:

字符显示

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有