时间:2023-11-01 15:46

人气:

作者:admin

晶圆术语

1.芯片(chip、die)、器件(device)、电路(circuit)、微芯片(microchip)或条码(bar):所有这些名词指的是在晶圆表面占大部分面积的微芯片图形;

芯片ECO流程

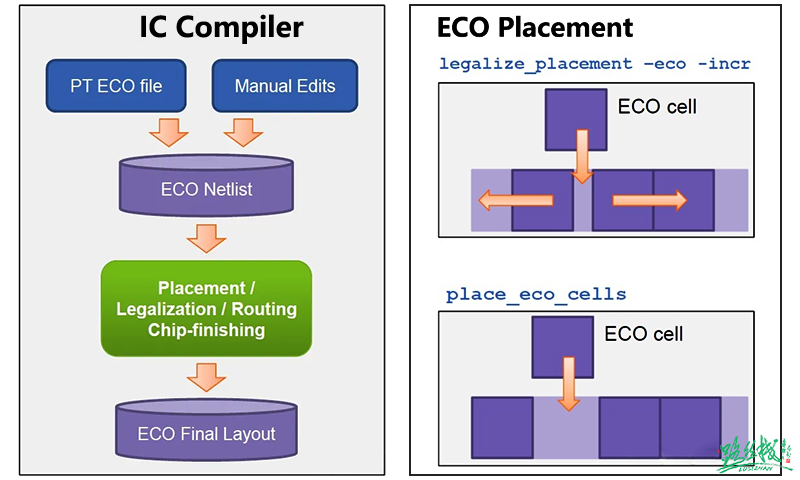

ECO 指的是Engineering Change Order,即工程变更指令。ECO可以发生在Tapeout之前,过程中,或者之后;Tapeout之后的ECO,改动少的可能仅需要改几层Metal layer,改动大可能需要动十几层Metal layer,甚至重新流片。ECO 的实现流程如下图所示:

如果MPW或者FullMask的芯片,验证有功能或者性能缺陷,通过ECO对电路和标准单元布局进行小范围调整,保持原设计布局布线结果基本不变的前提下做小规模优化,修复芯片的剩余违例,最终达到芯片的签核标准。不能通过后端布局布线的流程来修复违例(重新走一遍流程太费时了),而要通过ECO的流程来进行时序、DRC、DRV以及功耗等优化。

上一篇:芯片的流片方式有哪几种

台积电如何为 HPC 与 AI 时代的 2.5D/3D 先进