时间:2024-02-28 13:44

人气:

作者:admin

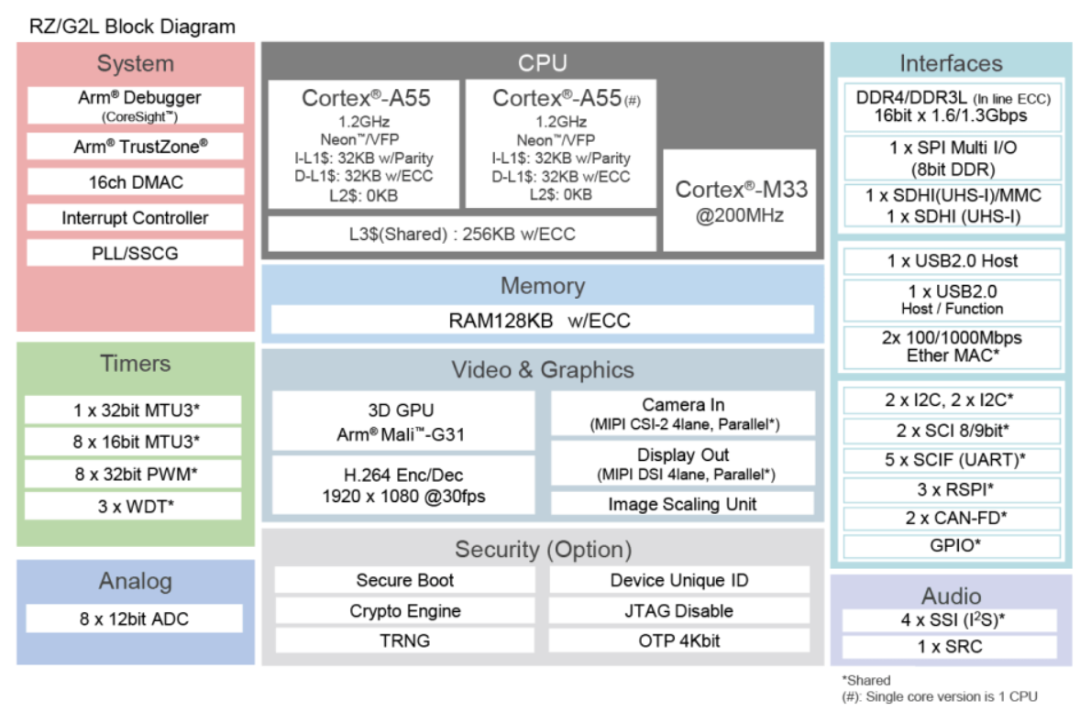

RZ/G2L微处理器配备Cortex-A55 (1.2 GHz) CPU、16位DDR3L/DDR4接口、带Arm Mali-G31的3D图形加速引擎以及视频编解码器(H.264)。此外,这款微处理器还配备有大量接口,如摄像头输入、显示输出、USB 2.0和千兆以太网,因此特别适用于入门级工业人机界面(HMI)和具有视频功能的嵌入式设备等应用。

ECC是一种用于检测和纠正内存数据中的错误的机制,用于高可靠性应用场景。

ECC有如下方案

边带ECC

内联ECC

片上ECC

链接ECC

从G2L框图可见,支持DDR in-line ECC功能。

RZ/G2L系列板上的内存控制器提供可选的ECC功能,可用于验证内存中的数据并在发生内存错误时纠正它们。内存控制器将检查所有读取事务中的数据以及校验错误。

ECC工作原理是创建独特的“校验码”,这些校验码是对称为“ECC数据字”的对齐数据段中的信息进行数学描述。

校验码始终与整个ECC数据字相关联,并且可以在内存控制器内部用于所有内存读取,以控制数据的准确性。“在线”ECC将这些校验码存储在内存中,该内存对用户不可见。

内存控制器将ECC错误定义为“可纠正的”或“不可纠正的”。可纠正的错误是校验码或数据中的一位错误。控制器使用综合特征来确定哪个位出现错误并可以纠正错误。不可纠正的错误是校验码或数据中的双位错误。在这种情况下,控制器可以识别校验码或数据中不正确的2位,但无法准确确定哪2位有错误,因此无法纠正错误。

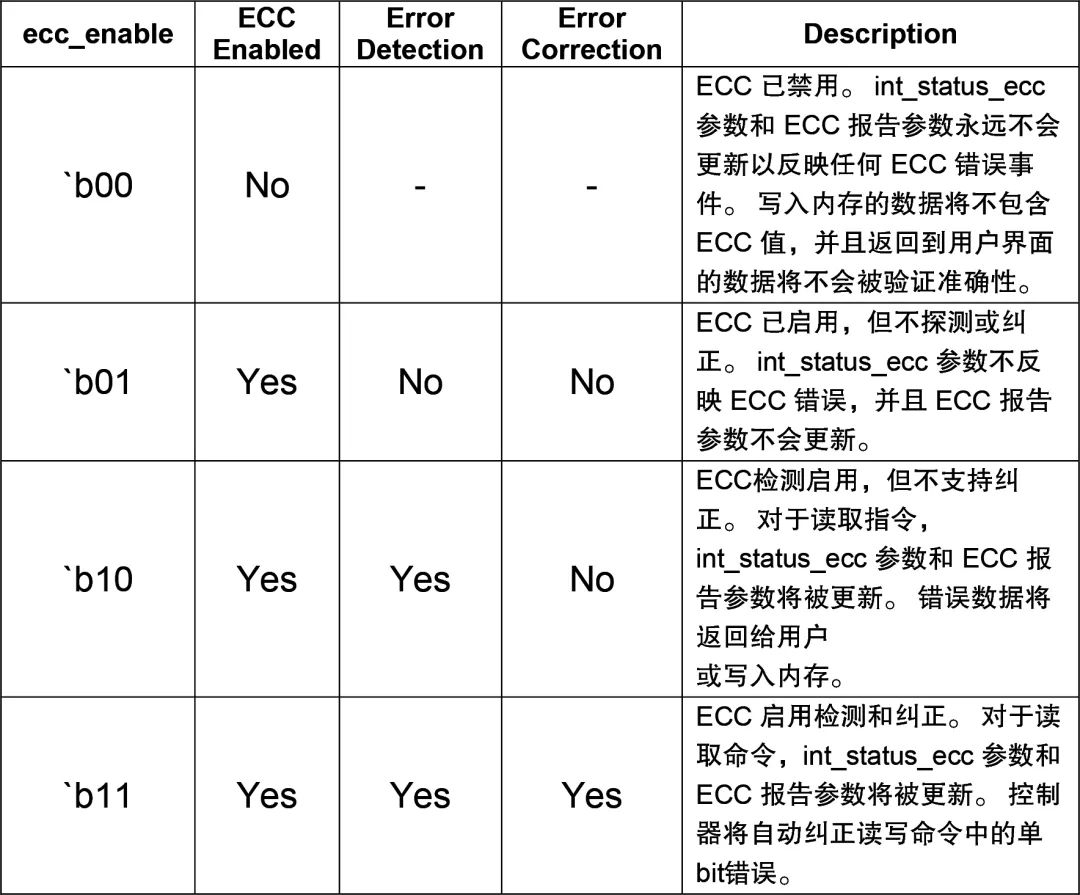

软件通过将ecc_enable参数设置为非零值来启用ECC。

控制器中的ECC功能由ecc_enable参数控制。该参数使能ECC,并设置上报和纠错行为。

ecc_enable参数含义详细说明:

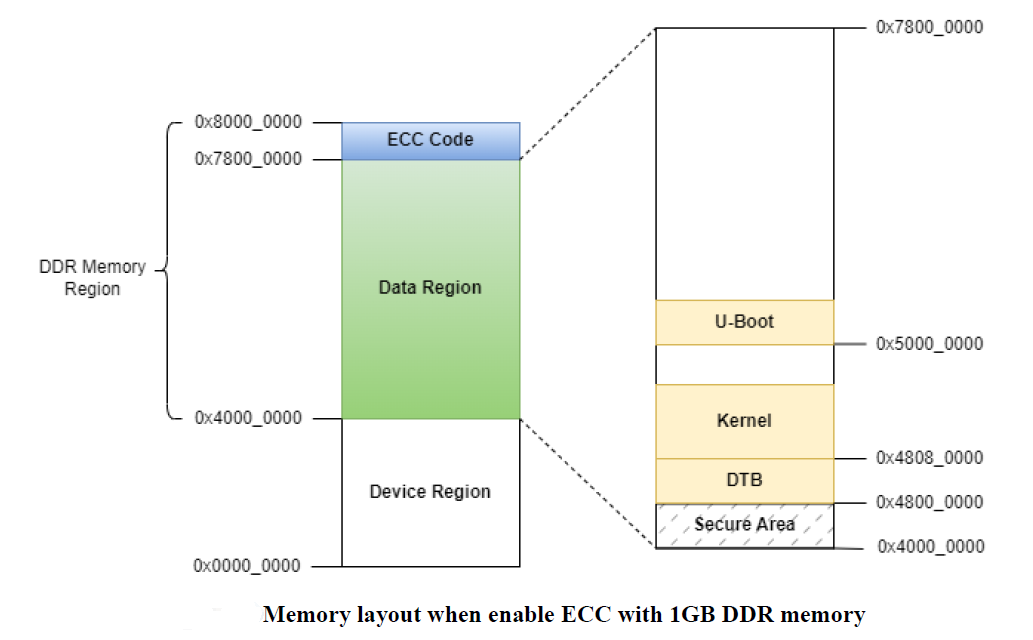

G2L内存控制器支持in-line ECC,其中内存区域的一部分(1/8)用于ECC存储。当ECC功能启用时,内存控制器将分配顶部1/8内存区域来存储ECC校验码。并且不允许用户访问该区域。

例如,当DDR内存为1GB时,启用ECC功能时内存布局如下图所示。假设DDR内存映射到系统总线,并以地址0x4000_0000开始,以0x7FFF_FFFF结束。要使用的数据区域为0x4000_0000 – 0x77FF_FFFF。顶部1/8内存区域是0x7800_0000 – 0x7FFF_FFFF (128MB) 将用于保存ECC校验码。

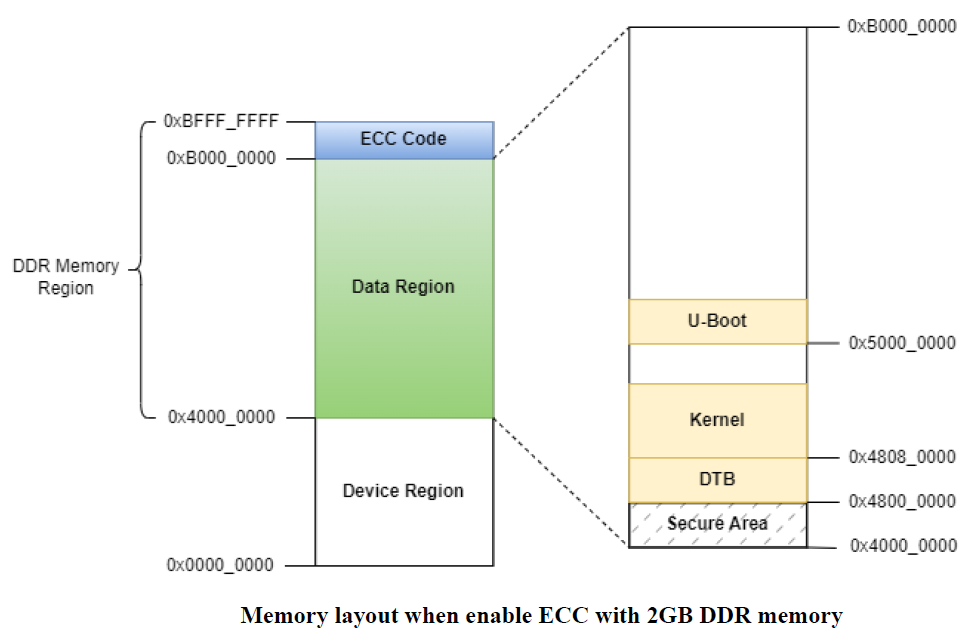

当DDR内存为2GB时,启用ECC功能时内存布局如下图。

假设DDR内存映射到系统总线,并以地址0x4000_0000开始,以0xBFFF_FFFF结束。

要使用的数据区域为0x4000_0000 – 0xAFFF_FFFF。顶部1/8内存区域是0xB000_0000 –

0xBFFF_FFFF(256MB) 将用于保存ECC校验码。

以上概要介绍ECC功能和机制,后续会介绍软件使用配置。

审核编辑:刘清

NVIDIA RTX PRO 4500 Blackwell GPU测试分析