时间:2023-09-01 15:01

人气:

作者:admin

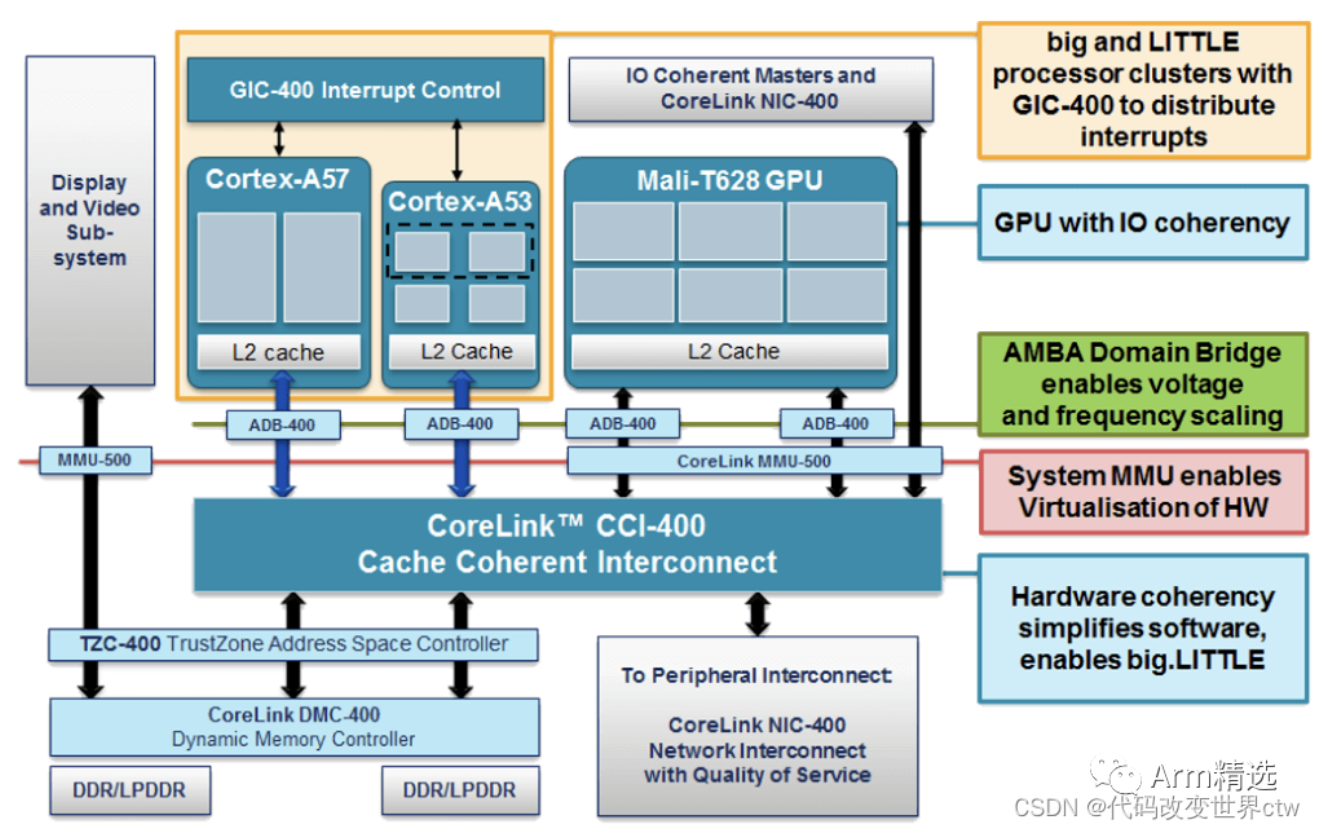

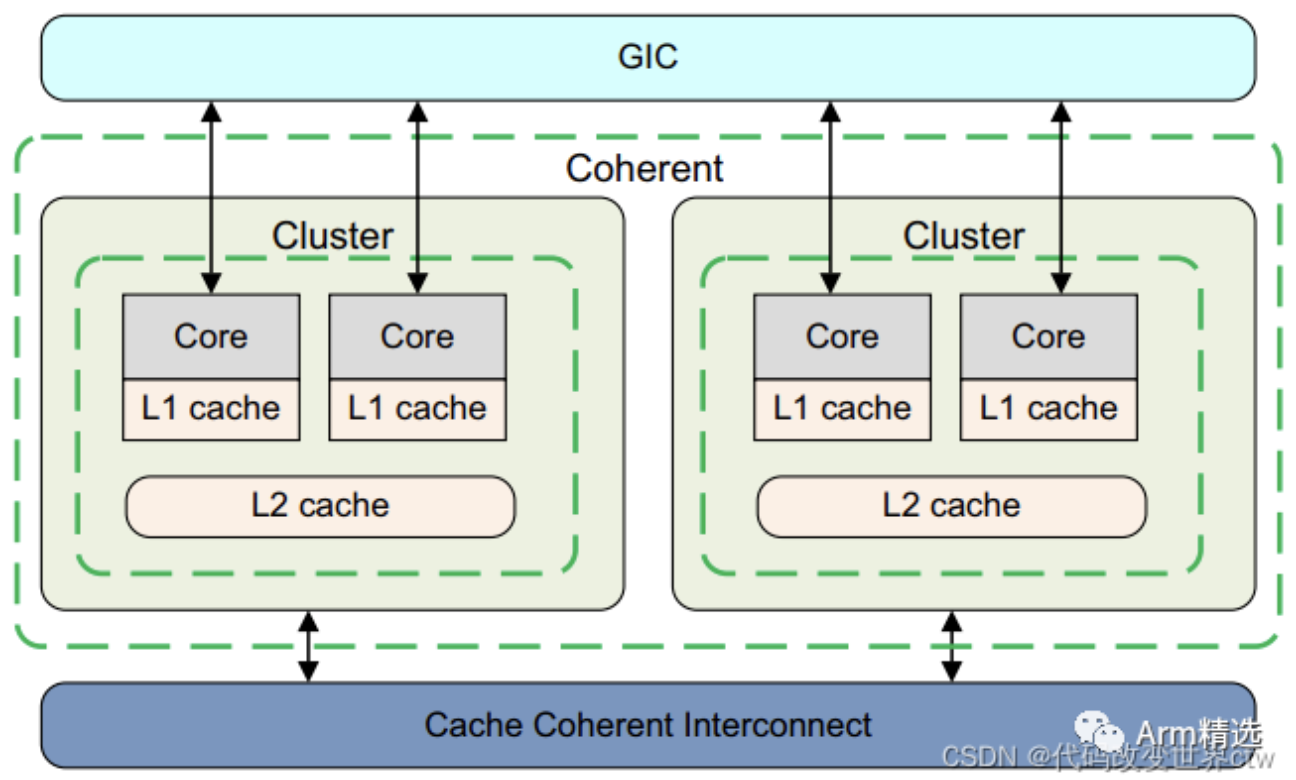

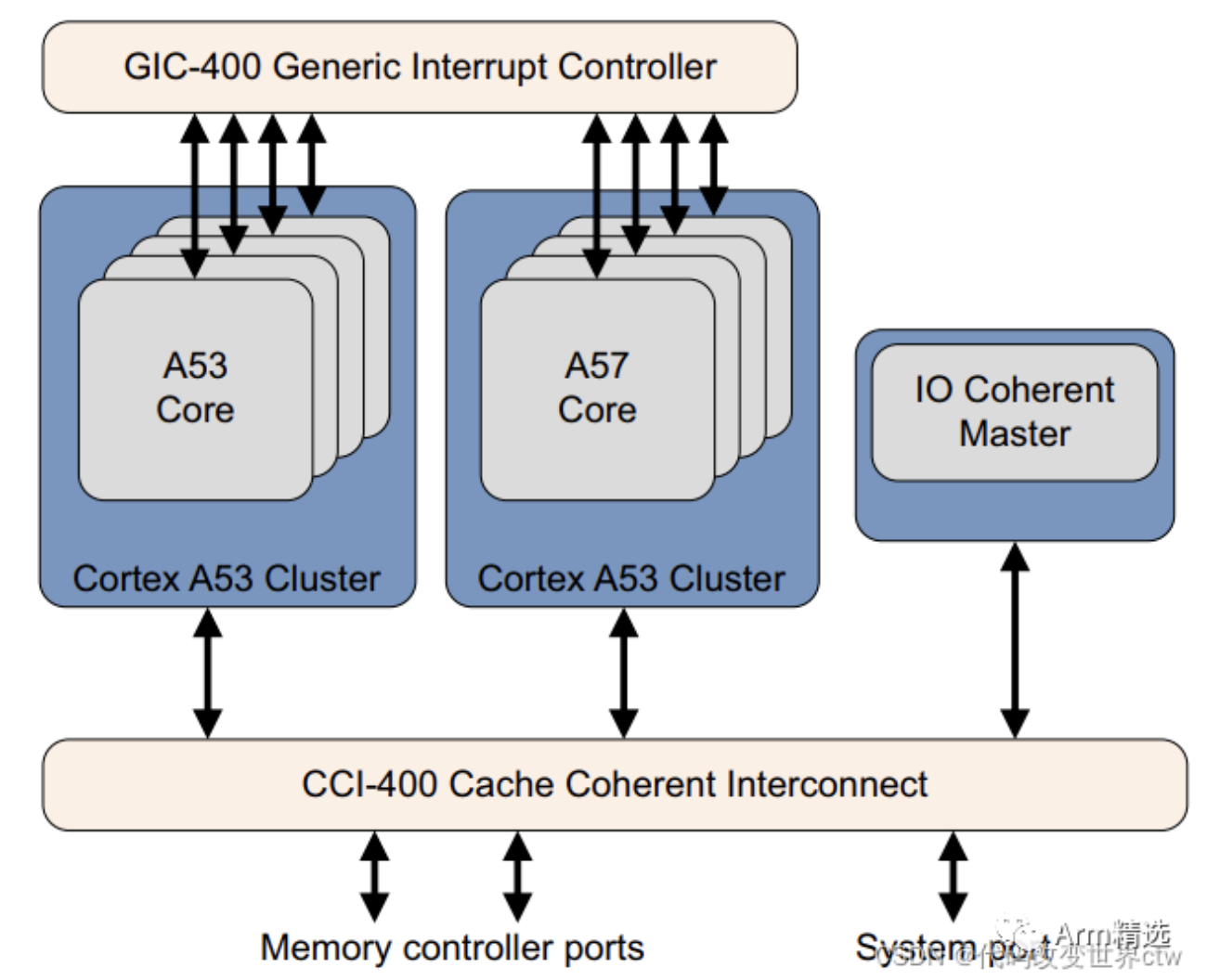

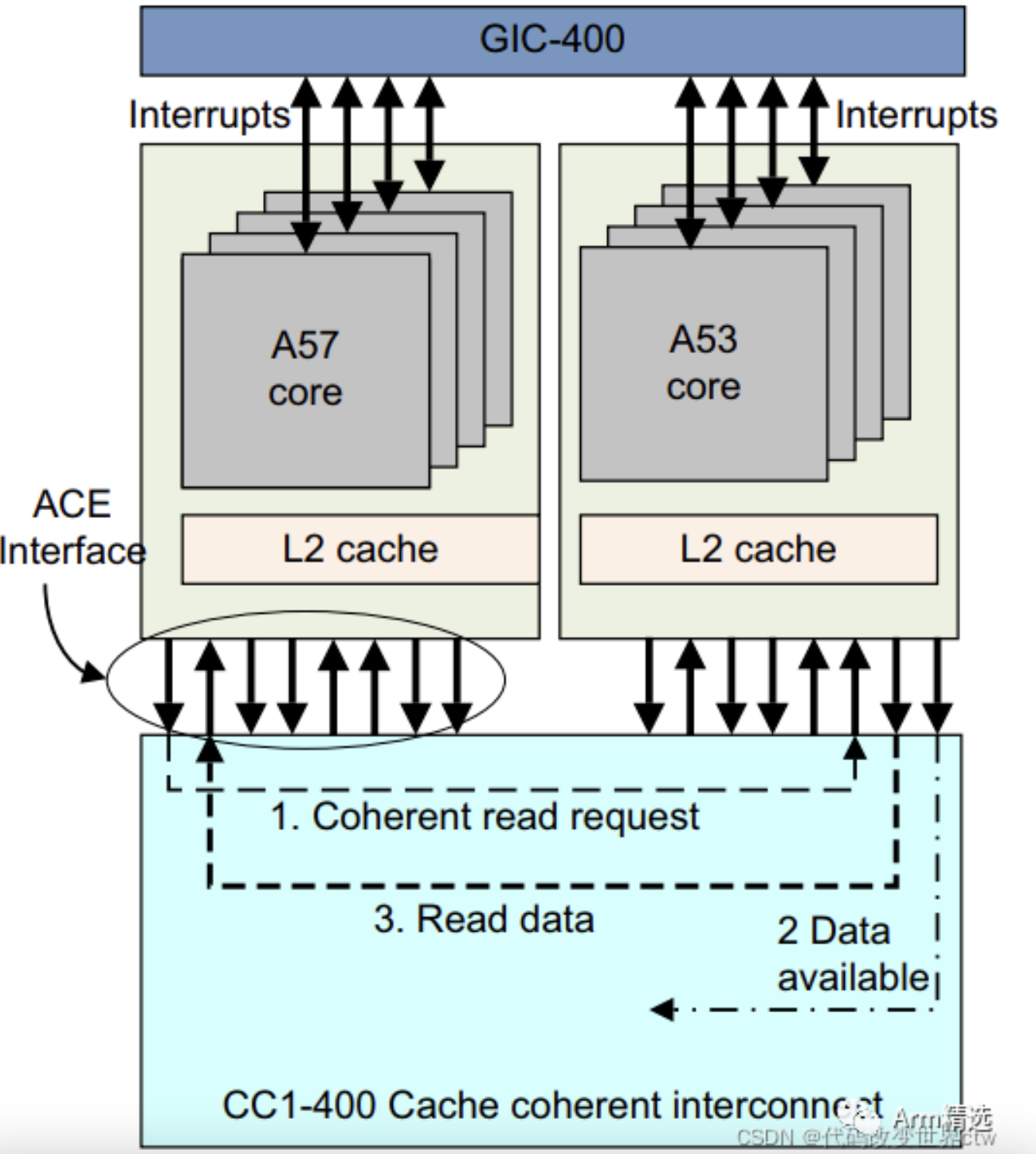

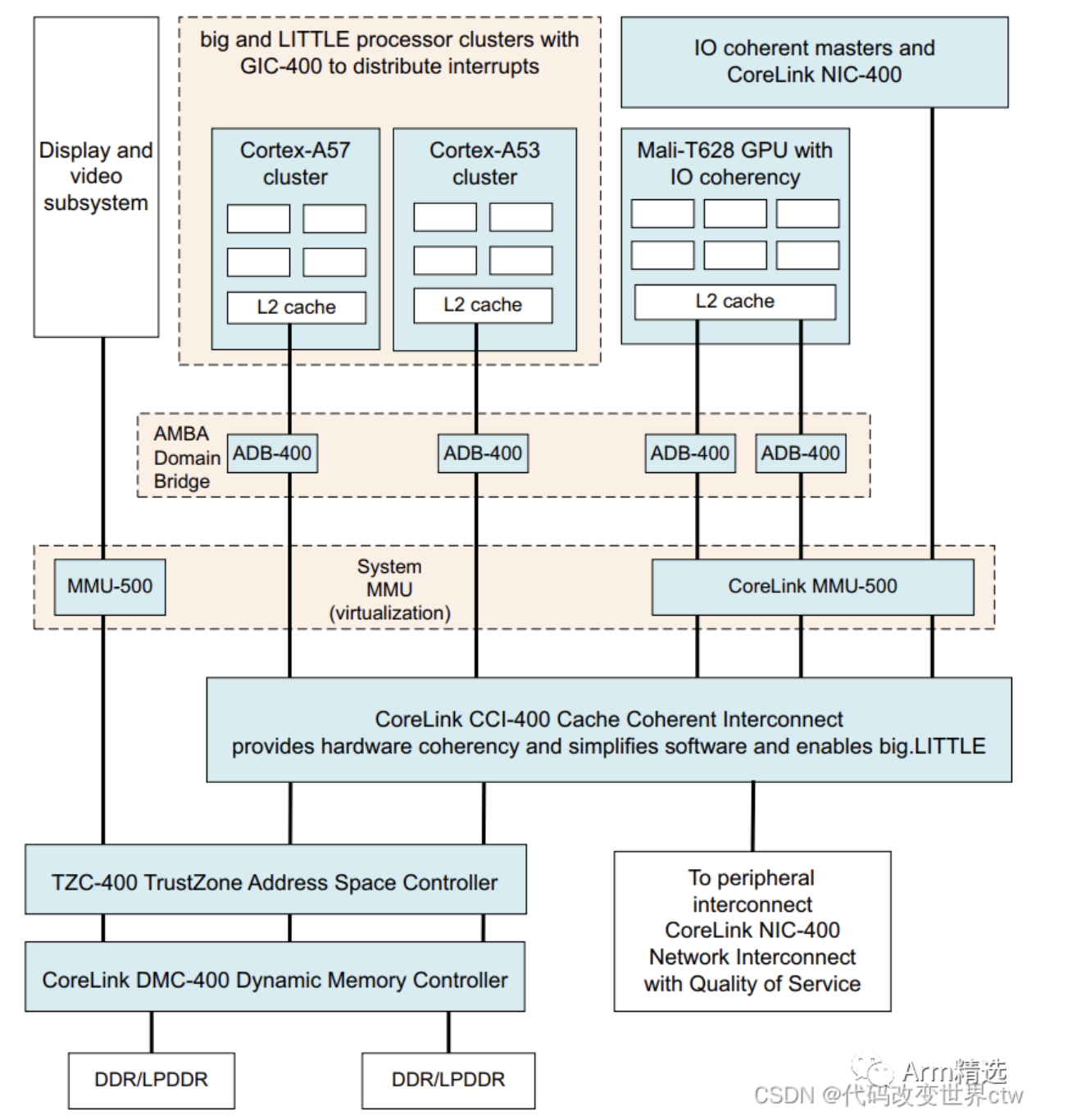

以下是一张比较早期的经典的big-LITTLE的架构图。

图1

图2

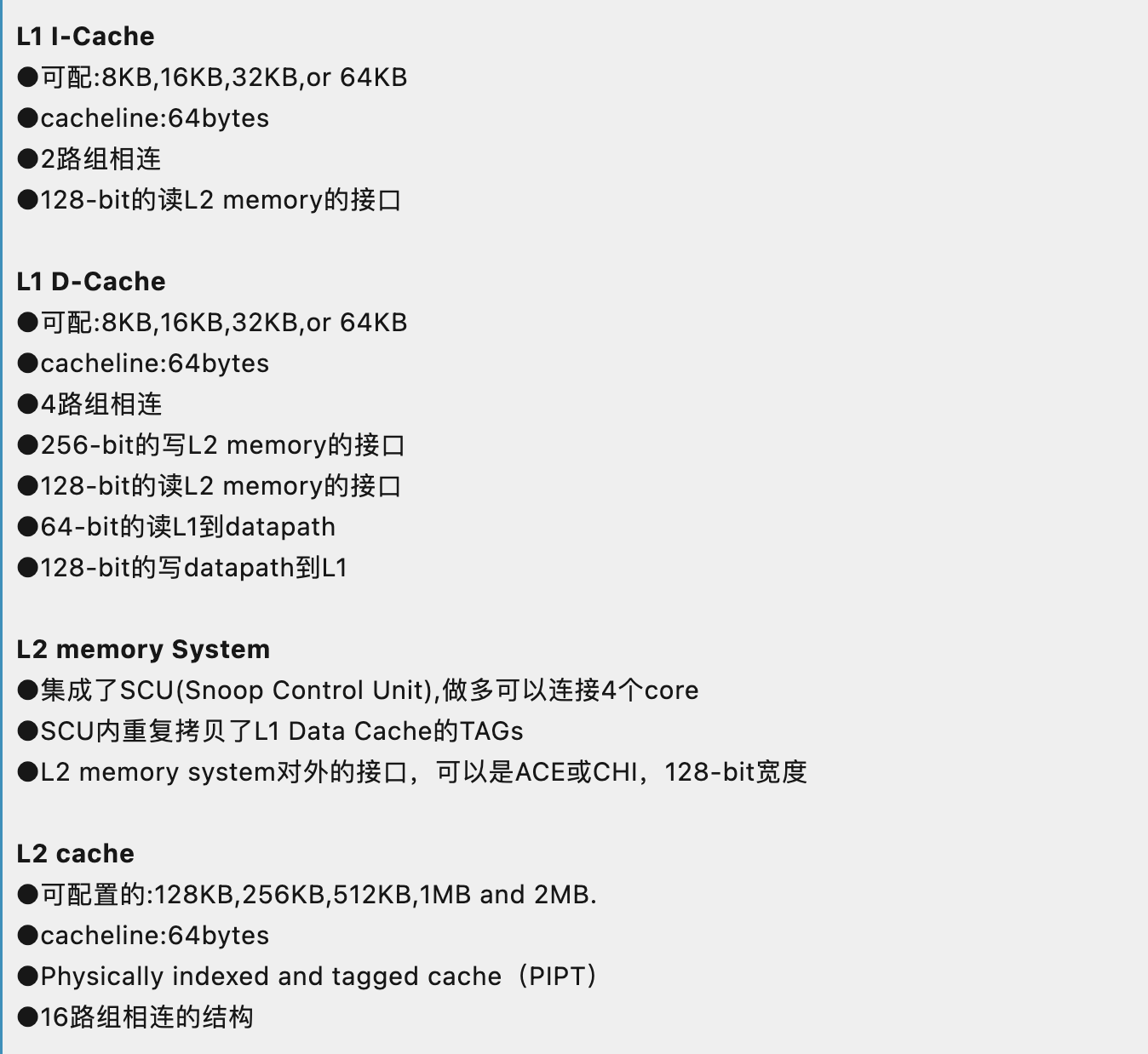

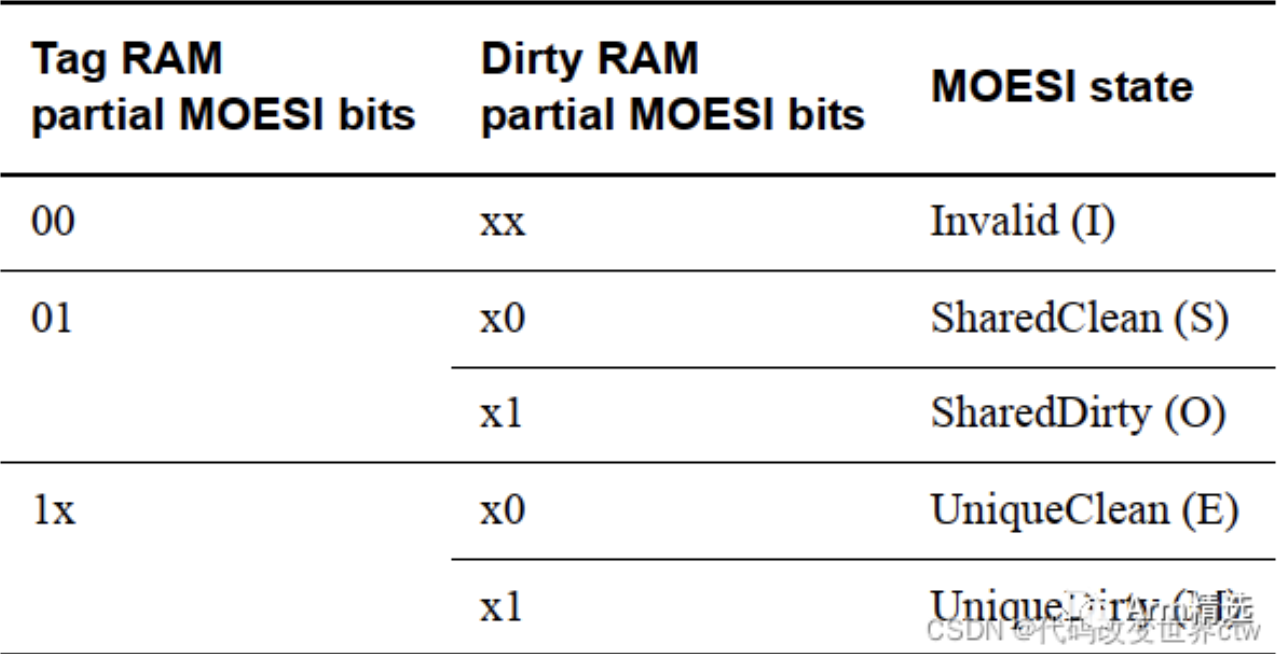

A53的L1 Data cache遵从的是MOESI协议,如下所示在L1 data cache的tag中存有MOESI的标记位。

图3

图4

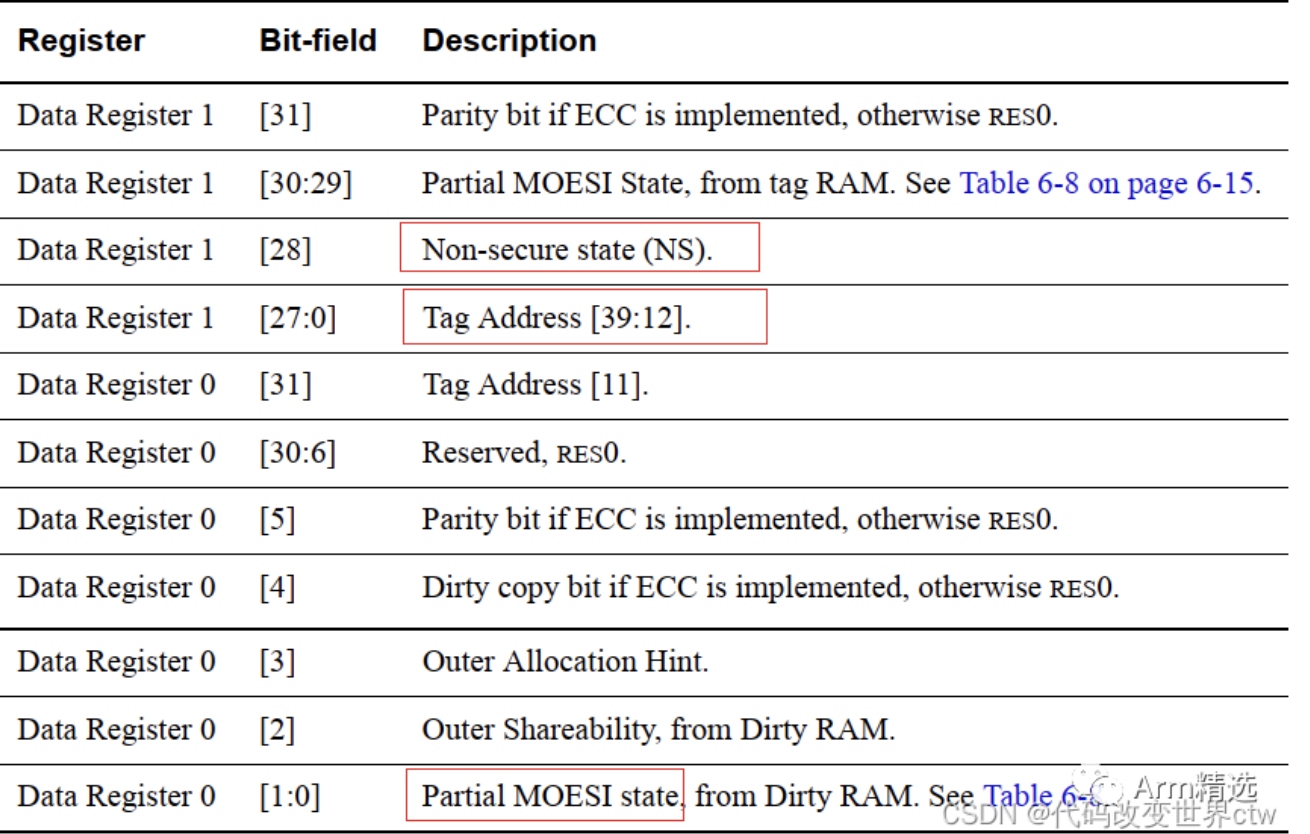

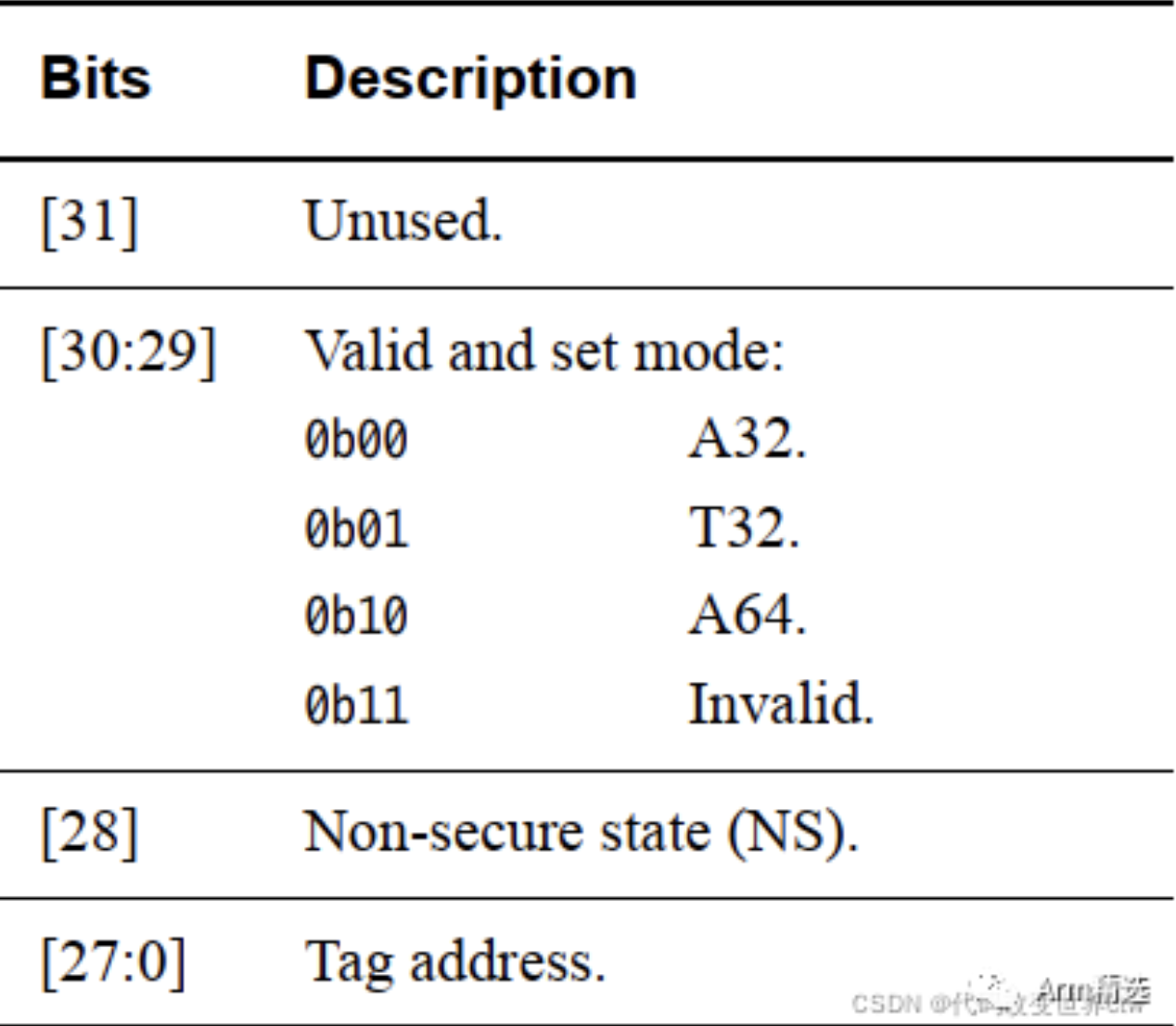

L1 instruction cache是只读的,所以也就无需硬件维护的多core之间instruction cache的一致性,所以也就无需组从MOESI协议,以下展示了 * L1 Instruction cache的TAG,其中标记为很少,无MESI标记位。

图5

图6

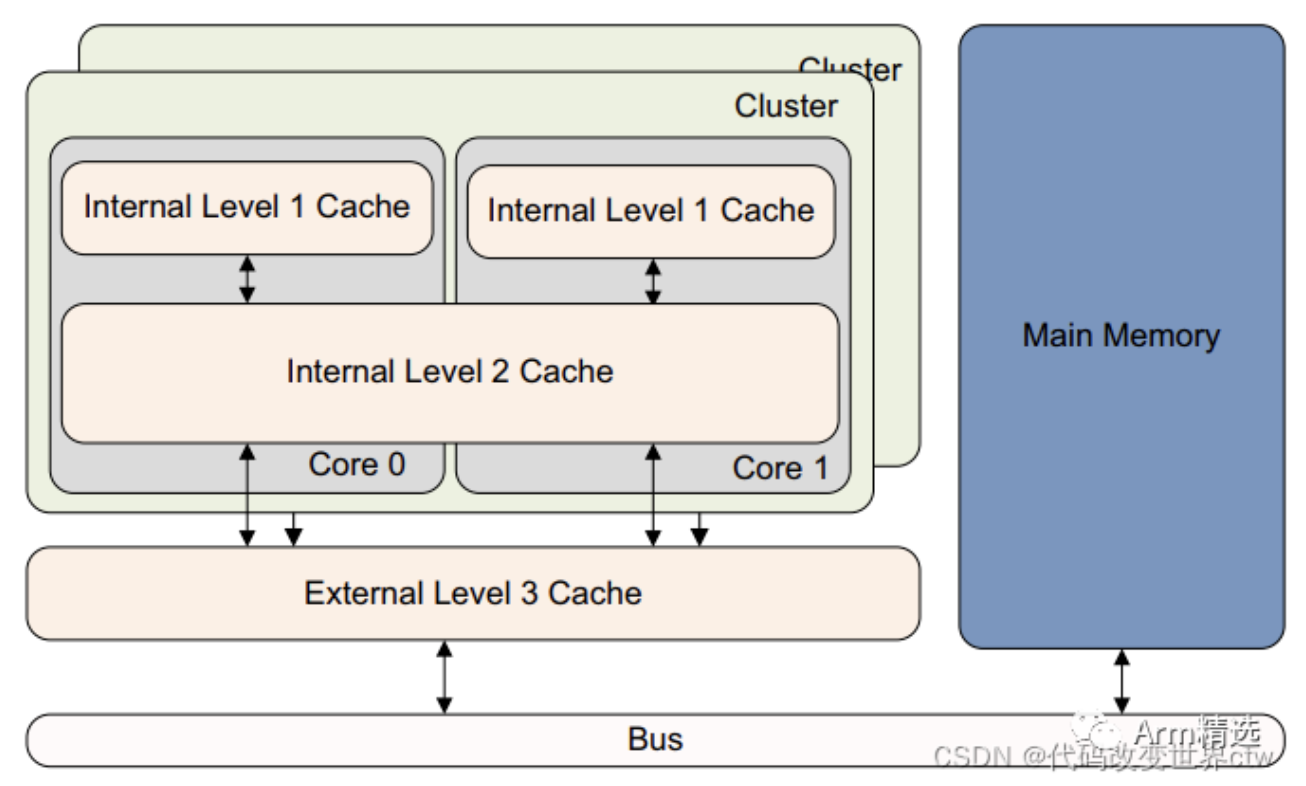

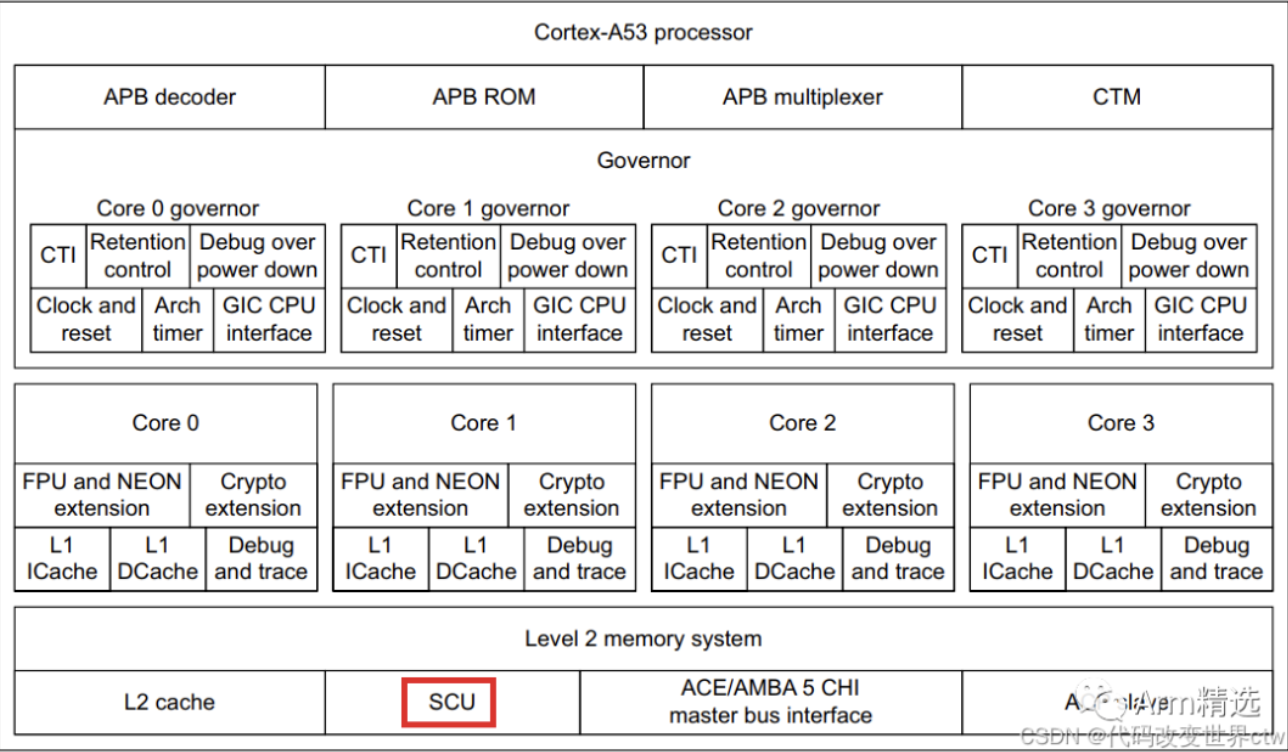

在bit.LITTLE架构中,在Cluster中,有一个SCU单元,SCU单元主要是执行和维护L1 cache的一致性(MESI协议或其变体如MOESI协议)。

图7

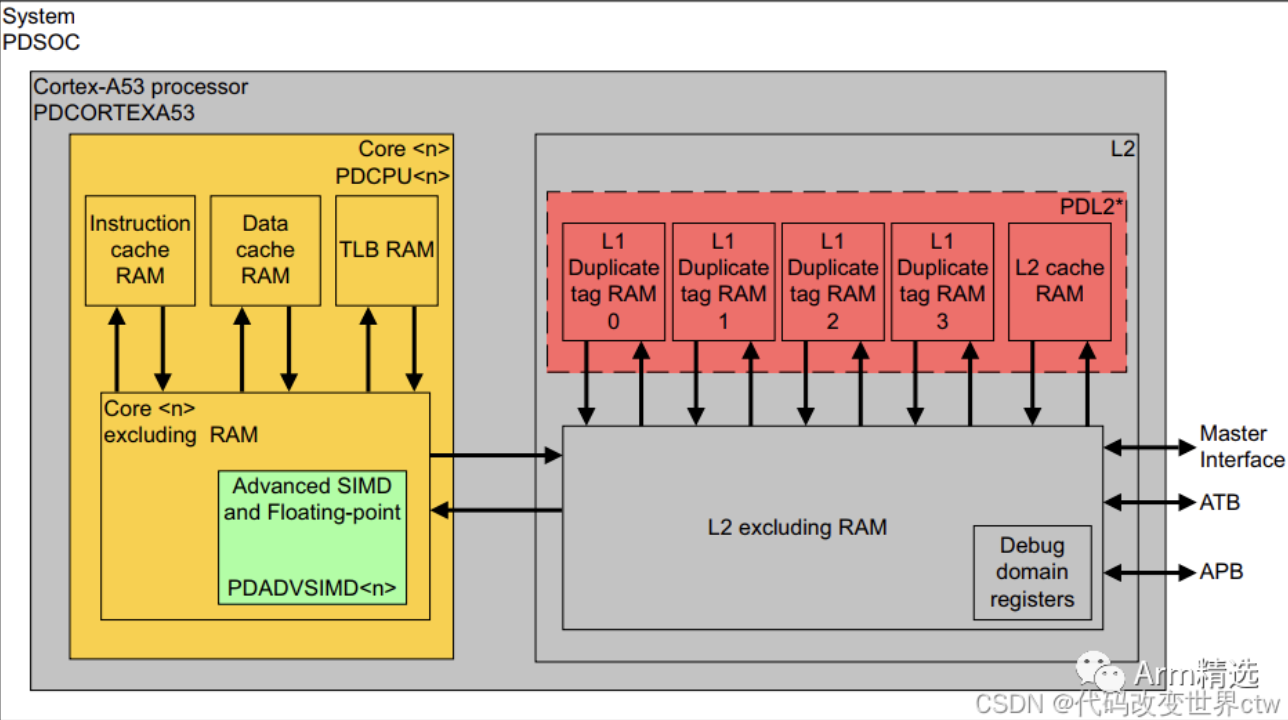

在L2 Memory System的中,除了包含L2 cache,也会包含L1 Duplicate tag RAM(这里指的其实是L1 Data Cache Tags)。

图8

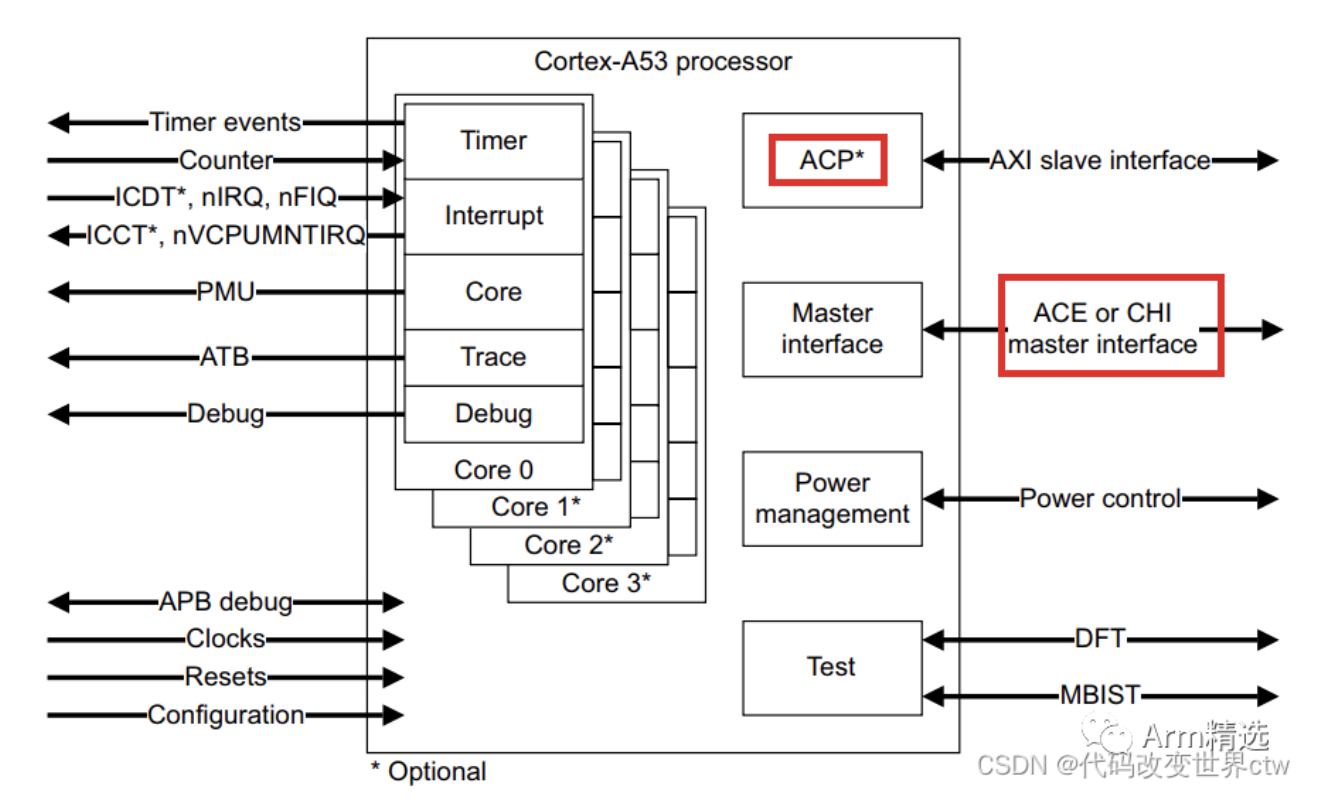

cluster和外界的接口,可以是ACE或CHI(目前常用的是ACE,后面的趋势可能是CHI)。

图9

图10

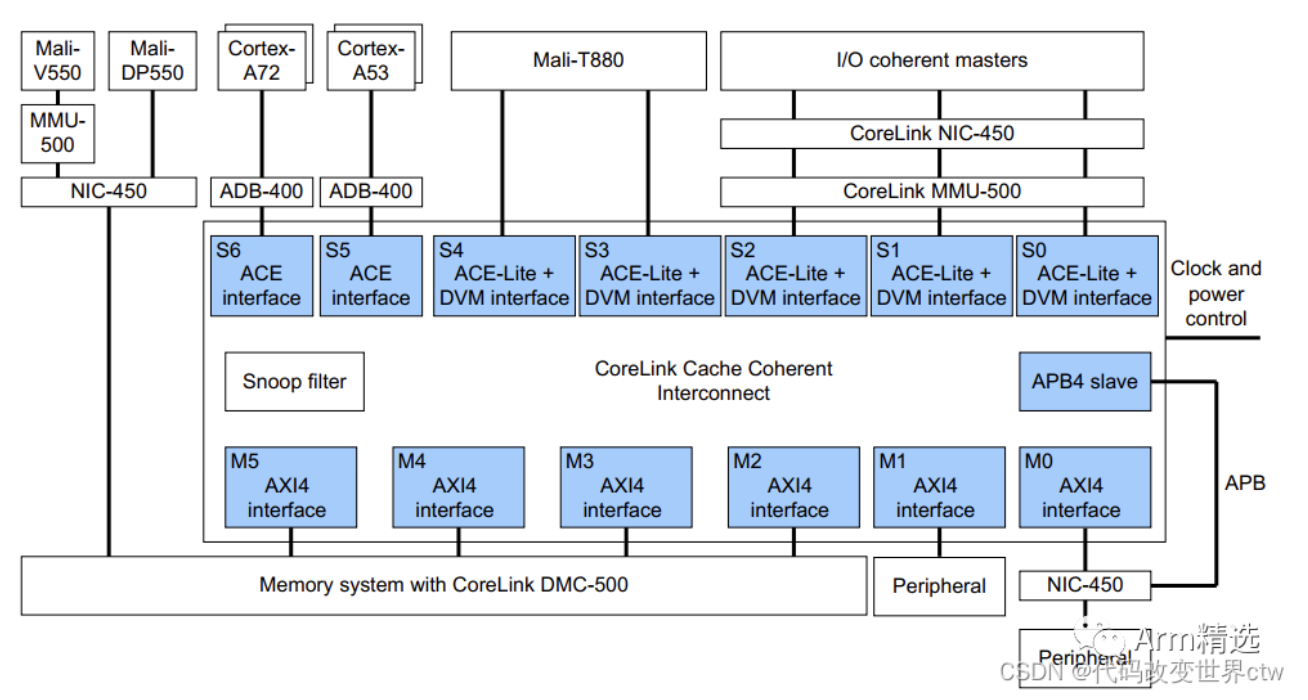

CCI-550包含一个包容性监听过滤器(snoop filter),用于记录存储在ACE主缓存。

侦听过滤器可以在未命中的情况下响应侦听事务,并侦听适当的主控只有在命中的情况下。Snoop过滤器条目通过观察来自ACE主节点的事务来维护以确定何时必须分配和取消分配条目。

侦听过滤器可以响应多个一致性请求,而无需向所有人广播ACE接口。例如,如果地址不在任何缓存中,则监听过滤器会以未命中和将请求定向到内存。如果地址在处理器缓存中,则请求被视为命中,并且指向在其缓存中包含该地址的ACE端口。

图11

图12

图13

NVIDIA RTX PRO 4500 Blackwell GPU测试分析