时间:2022-11-08 10:08

人气:

作者:admin

自昊芯推出专题讲解SCI串口通讯奇偶校验,分为两期讲解,上期主要讲解标准SCI模式下的奇偶校验,本期主要讲解增强FIFO模式下的奇偶校验。

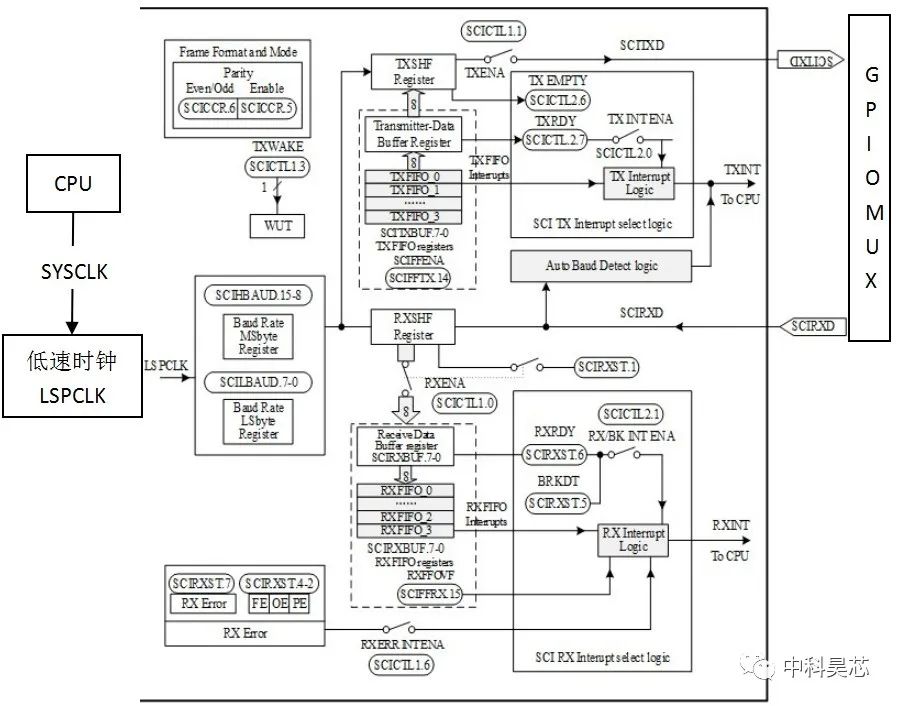

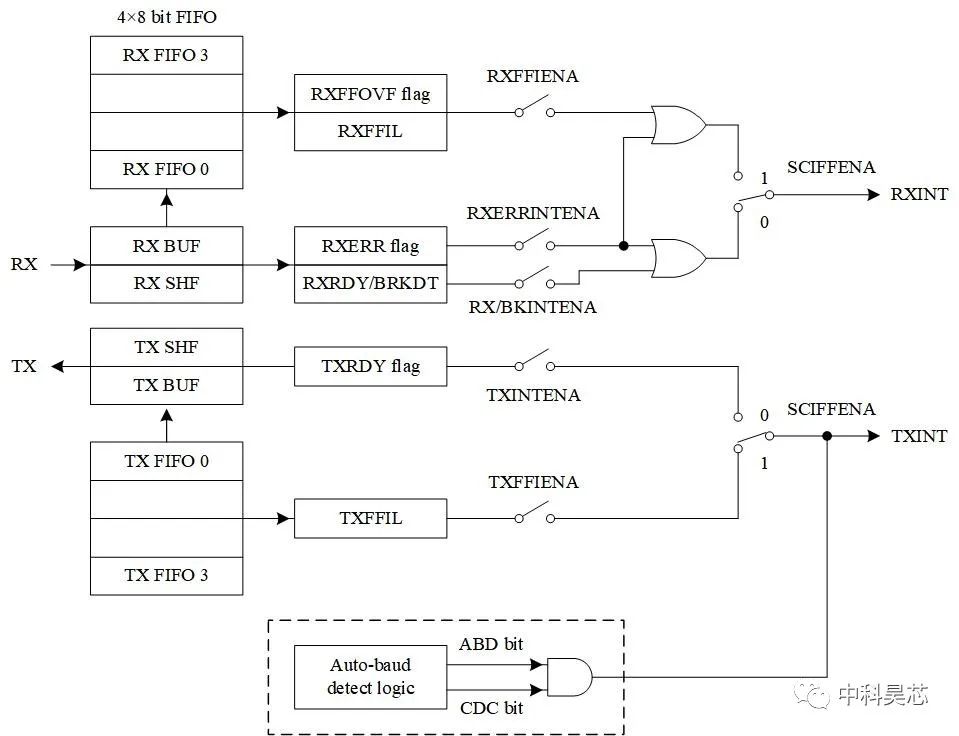

HX2000系列SCI模块与中断框图如下,可通过SCICCR[PARITYENA]使能,启动奇偶校验;采用SCICCR[PARITY]选择,使用奇或偶校验,对每个字符增加一个额外的校验位,以校验收发数据的二进制码中“1”的个数,校验收发数据的一致性;FIFO模式下校验原理与标准模式一致,但收发数据校验位不一致时,仅置位SCIRXBUF[SCIFFPE]输出错误信号。

由此设计SCI串口增强FIFO通信校验实例:采用SCI与串口CH340,通过串口调试助手,向CPU发送任意一组四字节数据,CPU接收所发送的数据,通过按键控制,选择奇或偶校验,校验收发数据的一致性,硬件连接如下图所示:

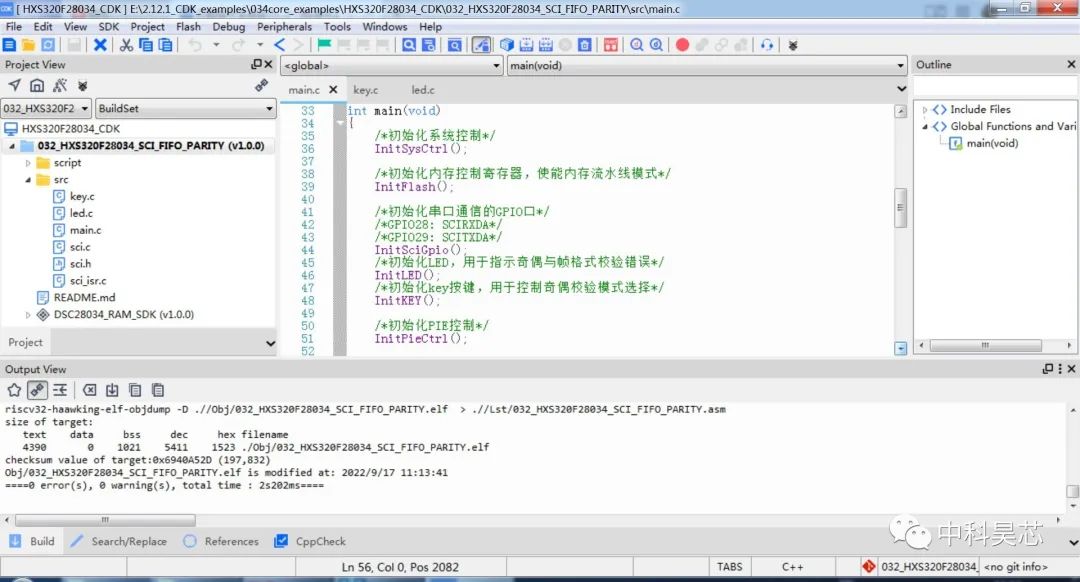

基于以上分析,在CDK上开发SCI串口增强FIFO通信校验,代码包括:SCI GPIO外设引脚配置,SCI增强FIFO功能与校验配置程序,发送、接收与校验程序,主程序调用执行。主要代码如下:

1.intmain(void)2.{3./*初始化系统控制*/4.InitSysCtrl();5./*初始化内存控制寄存器,使能内存流水线模式*/6.InitFlash();7./*初始化串口通信的GPIO口:GPIO28: SCIRXDA,GPIO29: SCITXDA*/8.InitSciGpio();9.10./*初始化LED,用于指示奇偶与帧格式校验错误*/11.InitLED();12./*初始化key按键,用于控制奇偶校验模式选择*/13.InitKEY();14.15./*关闭PIE中断*/16.InitPieCtrl();17./*清除中断标志位*/18.IER=0x0000;19.IFR=0x0000;20./*初始化PIE中断向量表*/21.InitPieVectTable();22.23.EALLOW;24./*中断向量表入口地址SCIRXINTA,指向执行接收中断、校验模式选择与程序*/25.PieVectTable.SCIRXINTA=&sci_rx_isr;26.EDIS;27.28./*打开相应的PIE中断线*/29.IER|=M_INT9;30./*PIEGroup9,SCIRXINTA*/31.PieCtrlRegs.PIEIER9.bit.INTx1=1;32.33./*SCI增强FIFO配置:含奇偶校验*/34.Scia_Config(9600);35./*打开全局中断*/36.EINT;37.for(;;)38.{39.}40.return0;41.}CDK上开发SCI串口增强FIFO通信校验程序,编译结果为:

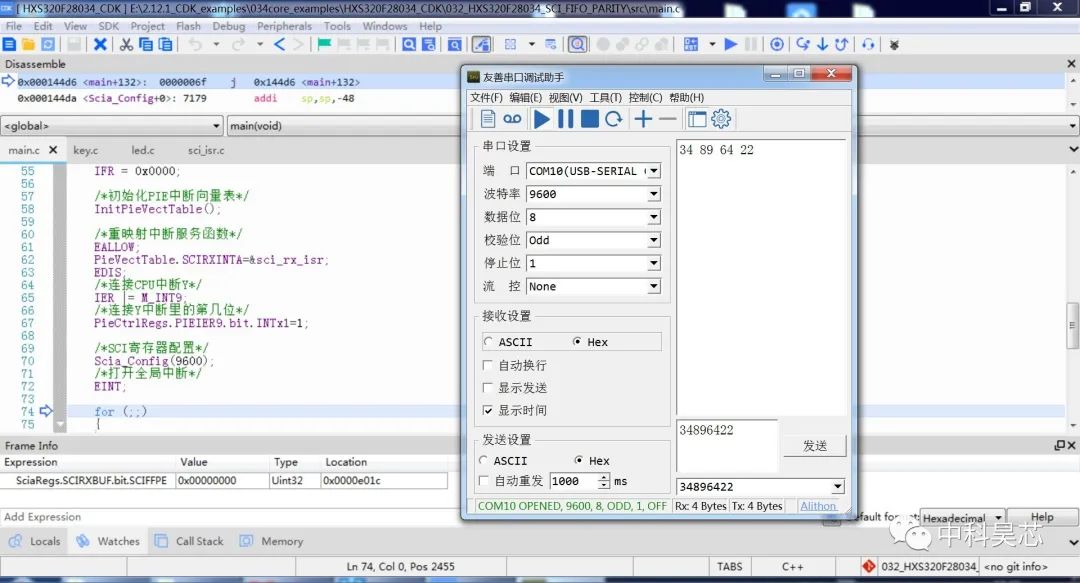

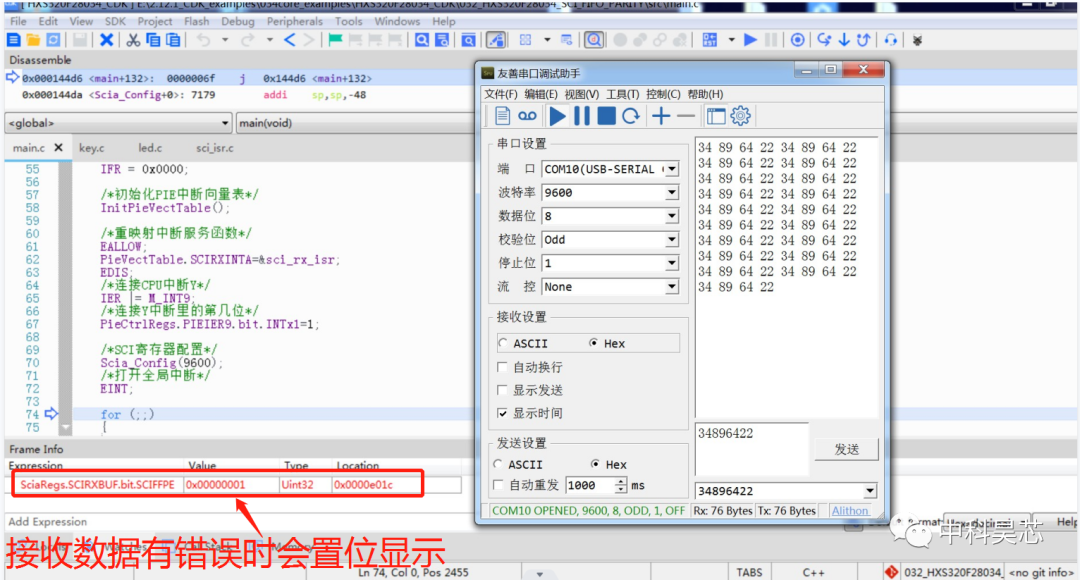

编译通过后,就可开始调试了,调试后,可通过串口调试助手查看发送与接收到的数据:

收发数据校验位不一致时,通过SciaRegs.SCIRXBUF.SCIFFPE置位输出错误信号:

NVIDIA RTX PRO 4500 Blackwell GPU测试分析