时间:2023-04-01 15:54

人气:

作者:admin

PF5020 PMIC外部DCDC 电源为MIMXRT1170 供电注意事项

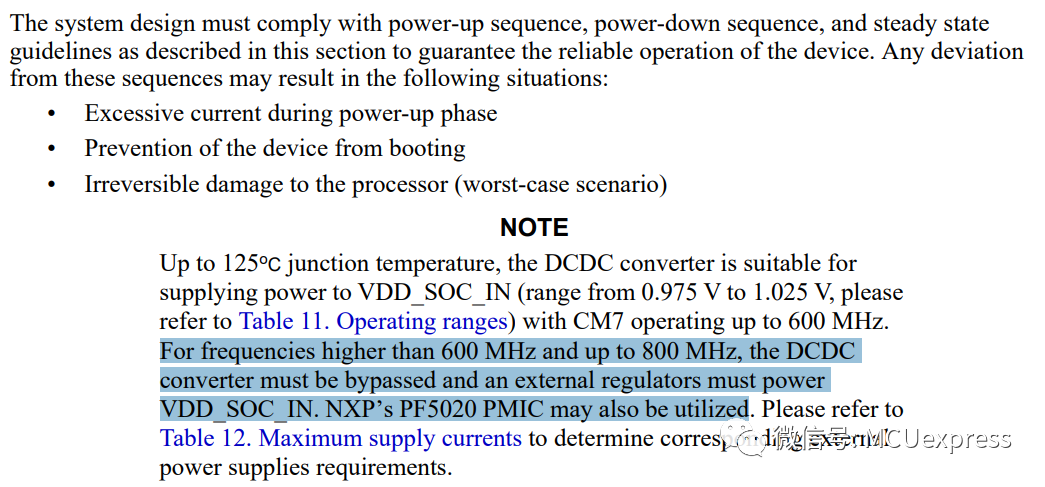

I.MX RT1170将先进的电源管理模块与DC-DC和LDO集成在一起,可降低外部电源的复杂性并简化电源时序。该处理器的片上DC-DC稳压器适用于高达105°C的消费和工业应用。

对于汽车应用,随着Tj增加到125°C,运行频率高于600Mhz-800Mhz,内核耗电可能超过内部DC-DC能力。在这种情况下,将i.MX RT1170与恩智浦PF5020 PMIC一起使用是非常合适的应用。

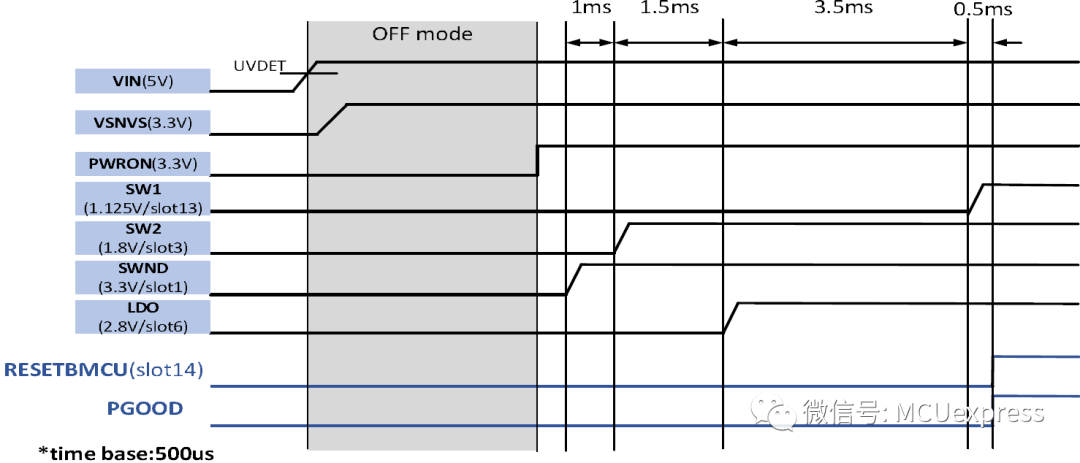

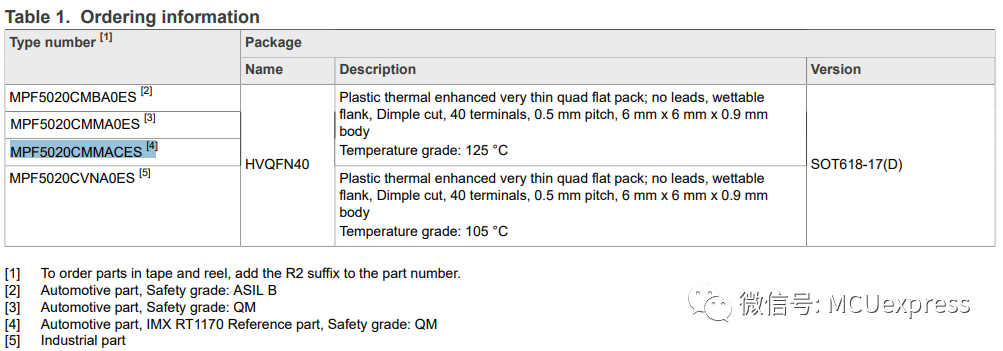

与 MIMXRT1170配套的 MPF5020CMMACES 默认出厂就内置了上电时序固件,通电就可以按照如下时序正常输出多路电压。

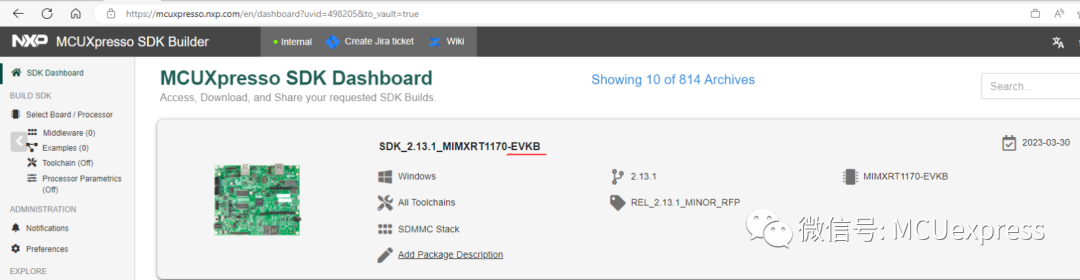

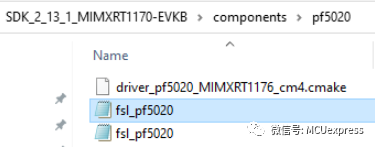

在 SDK2.13.1中内置了 pf5020的软件组件,如下图所示。

在如下文件夹中

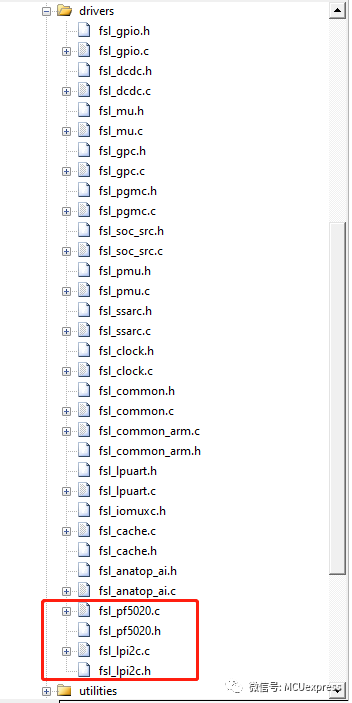

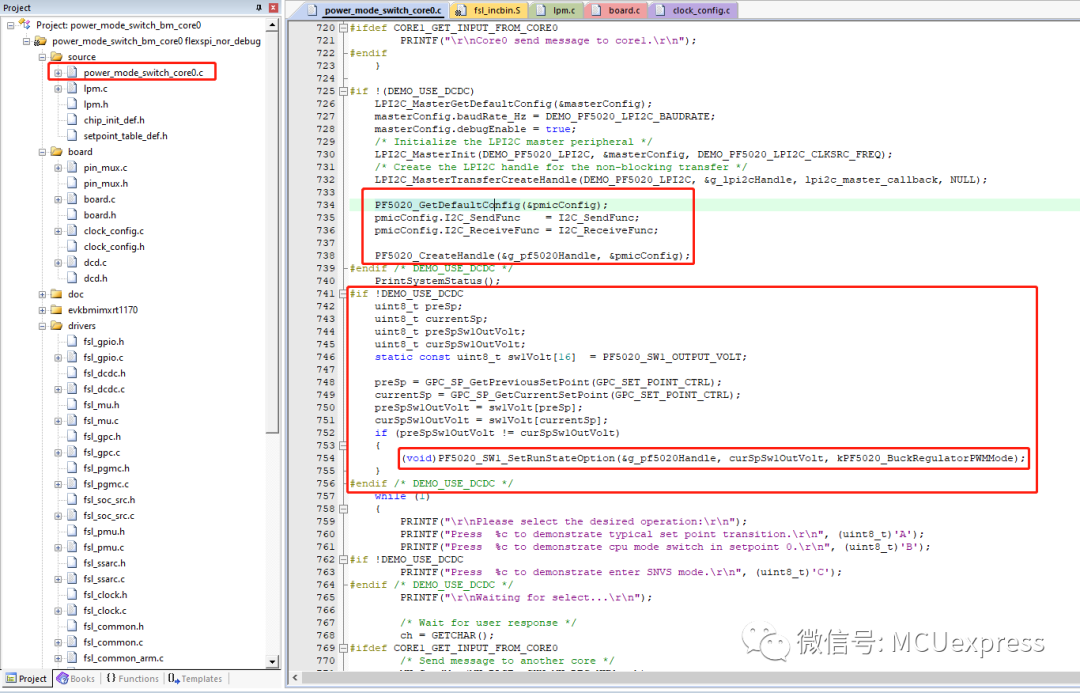

SDK/evkmimxrt1170/demo_apps/power_mode_switch/bm

添加 pf5020 驱动和 fsl_lpi2c 驱动到编译环境中。编译核 1 和内核0 项目即可使用了。

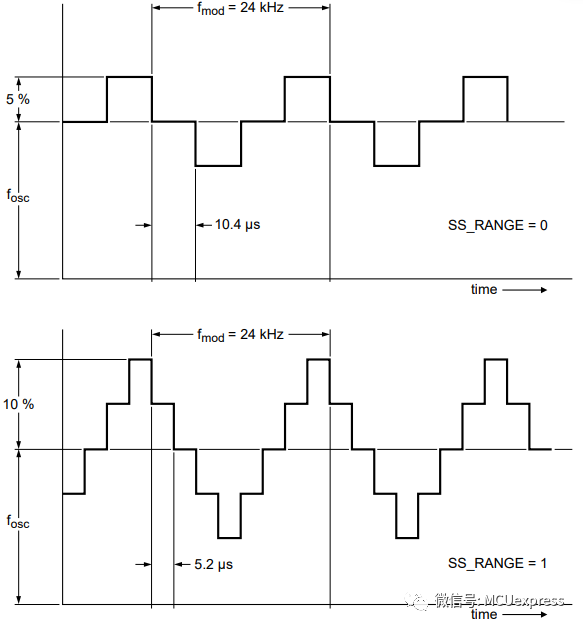

PF5020 PMIC的内部时钟提供了一个可编程的扩频功能,有窄扩频和宽扩频两个范围,有助于管理汽车应用中的EMC。

•当FSS_EN=1时,启用扩频。

•当FSS_EN=0时,频率扩展频谱被禁用。

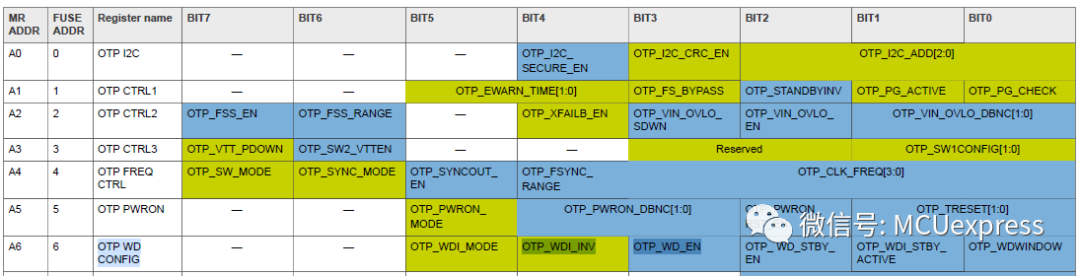

FSS_ EN位在加电时的默认状态可以经由OTP_FSS_EN配置。FSS_RANGE位提供了以下选择时钟频率范围。

•当FSS_RANGE=0时,最大时钟频率范围为±5%。

•当FSS_RANGE=1时,最大时钟频率范围为±10%。

上电时FSS_RANGE位的默认值可以通过OTP_FSS_RANCE位进行配置。当内部高频时钟用于生成开关调节器的开关频率时,以24kHz调制频率执行扩频。当启用外部时钟同步时,扩频将被禁用。

下图显示两种设置下扩频实现。

如果启用了频率扩展频谱,则应将开关调节器设置为PWM模式,以确保始终保持时钟同步。如果外部时钟同步被启用(SYNC_MODE=1),则不管FSS_EN 位的值如何,扩频都被禁用。

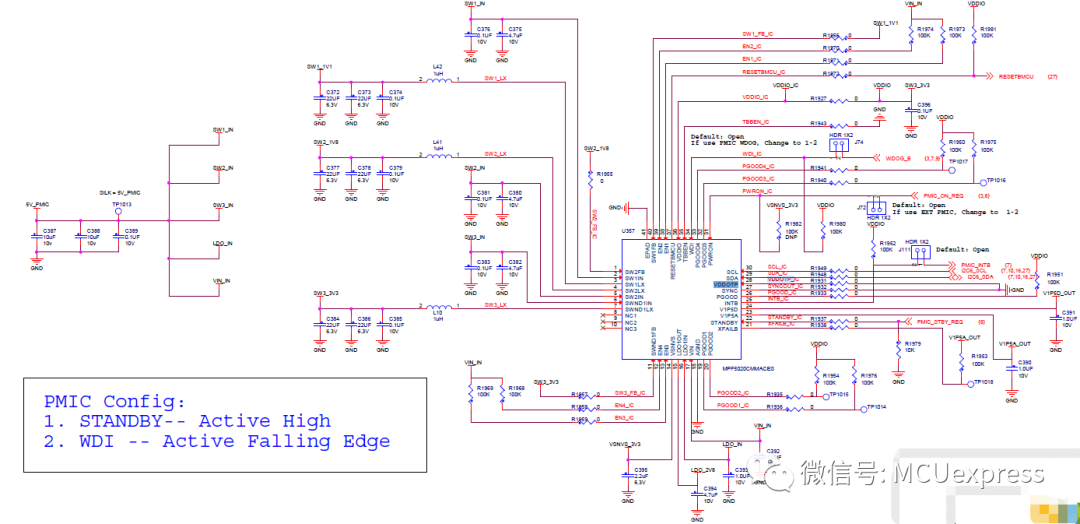

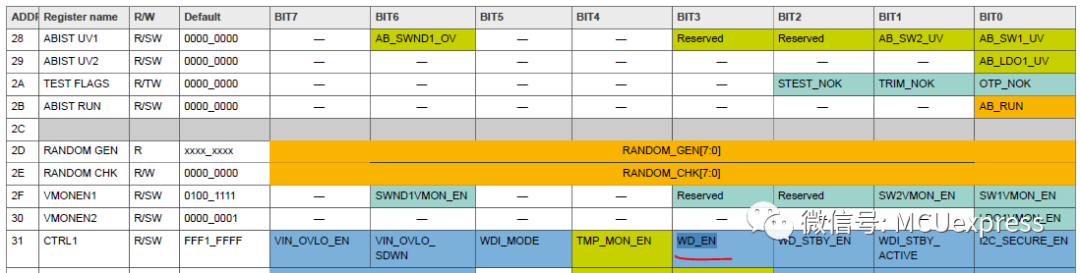

参考官方MIMXRT1170-EVKB的原理图如下。WDI脚是下降沿触发复位。

PWRON引脚(通过MIMXRT117X的PMIC_ON_REQ引脚控制)会控制整个PMIC的开启以及关闭,如果低功耗应用中,只保留PMIC PF5020的 VSNVS引脚给 MIMXRT117X的 SNVS模式供电,PMIC的其它电源关闭掉,可以用控制PWRON 关闭其他电源,SNVS引脚是常电一直有的,VSNVS的输出电源是不受PWRON的控制的。

如果低功耗下还需其它输出电压,可控制STANDBY管脚。EN1控制SW1,EN2控制SW2,EN3控制SWND1,EN4控制LDO1。EN1、EN2、EN3、EN4 不需单独控制。

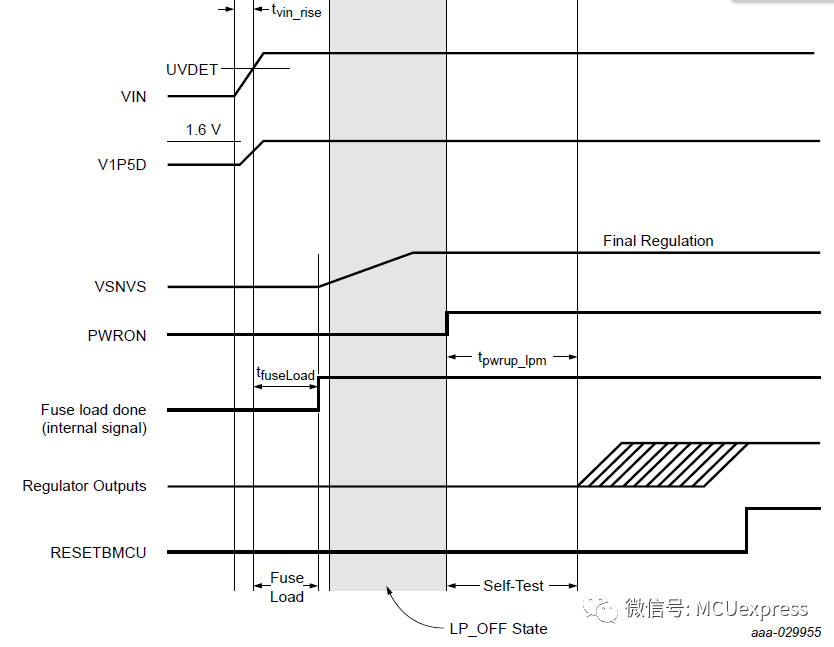

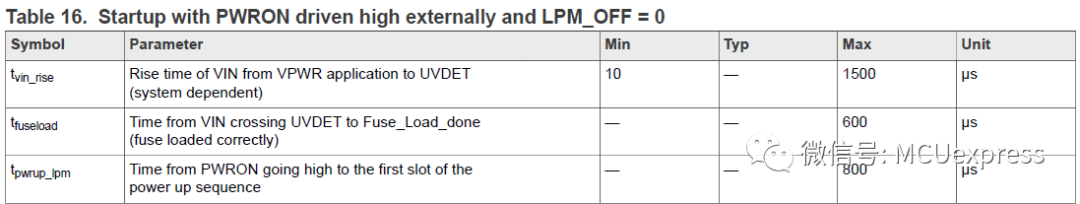

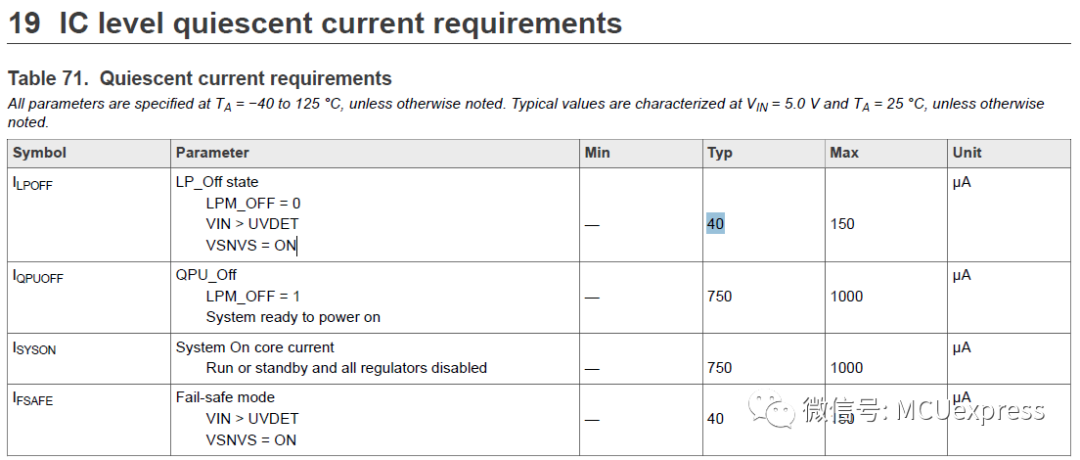

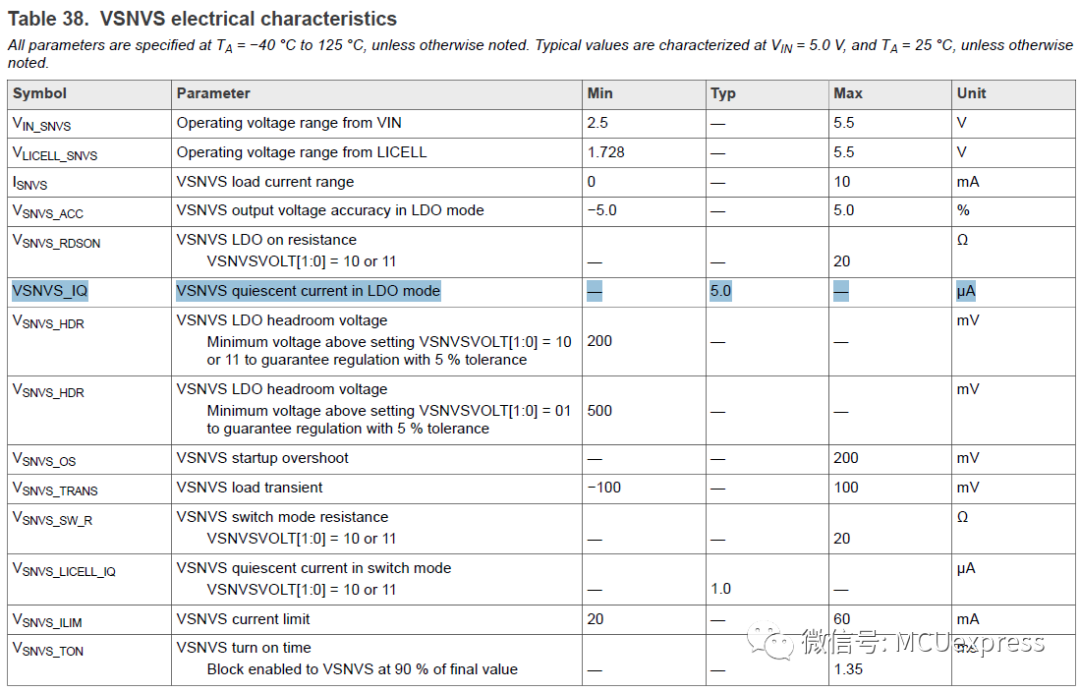

电源上电(VIN>UVDET)后,LPM_OFF位复位为0,因此PF5020 默认进入到LP_OFF状态,此时 VSNVS 模式下静态电流是 5uA,功耗极低。

严格按照VDDOTP和TBBEN引脚默认拉低到GND,WDI引脚上拉到100K,与外围MCU喂狗信号通过0欧电阻断开进行调试。

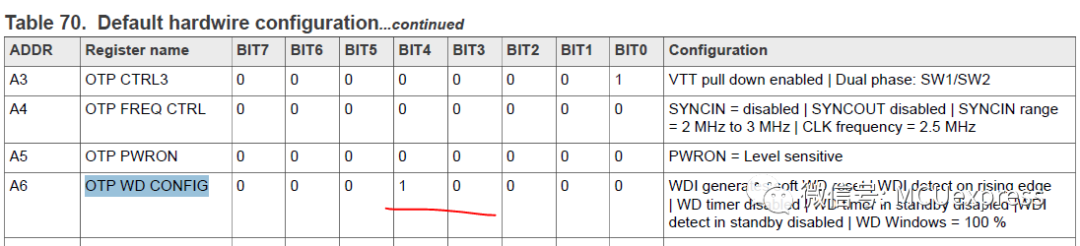

基于VDDOTP引脚上的电平状态,上电默认加载配置到功能I2C寄存器中。

•如果VDDOTP=GND,则 PF5020 从OTP寄存器加载配置。

•如果VDDOTP=V1P5D,则 PF5020 从默认硬件配置加载。

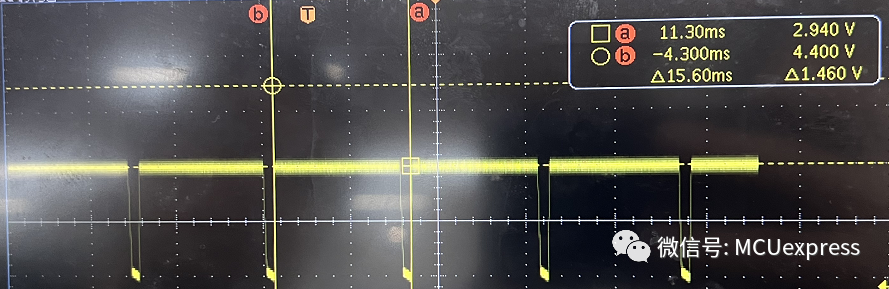

如果在WDI引脚出现有 15.6ms左右的复位脉冲,除了检查上述引脚以外,还需要监测VSNVS常电 3.3v是否输出正常?SWND1LX的3.3v输出电压是否正常? SW2LX提供系统电源的1.8v电压是否有正常输出? SW1LX(提供VDD_SOC_IN核电压)的1.1v电压是否有产生? 建议按照参考设计几路电源的输出端不要接任何的高频滤波磁珠等。

如果出现如下图类似的看门狗WDI引脚复位脉冲的话,SW1LX和SW2LX的输出电压不会是正常的输出电压。当出现类似的异常波形,可以重点看看文中绿色字体部分的内容。

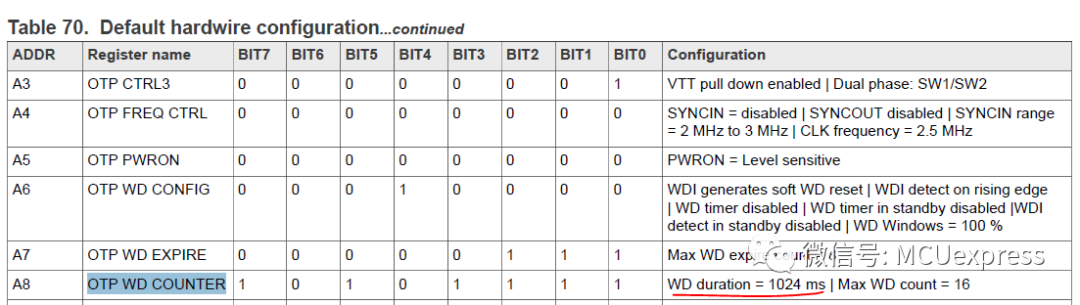

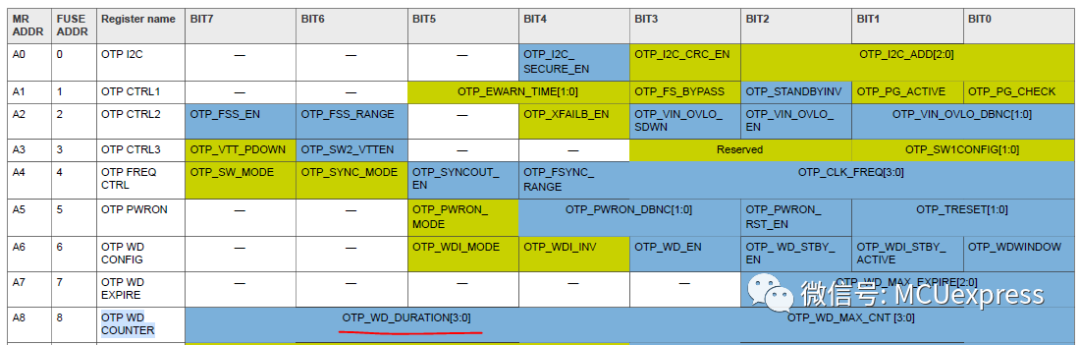

默认WD_EN=1,内部看门狗定时器操作被启用。

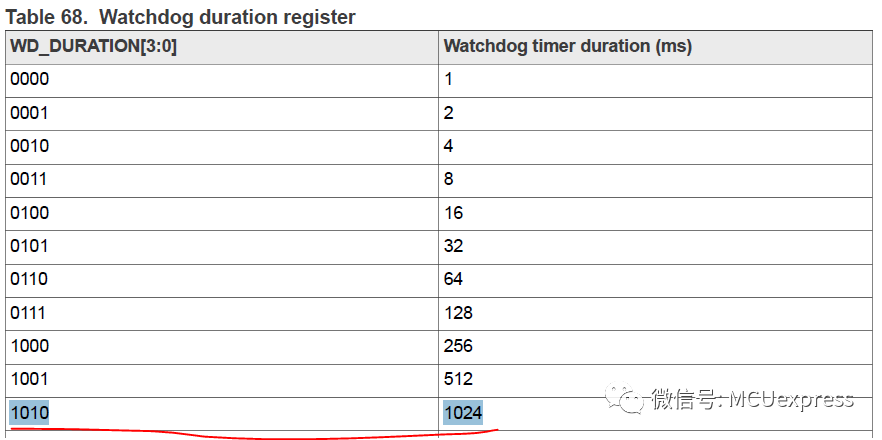

看门狗窗口持续时间选择初始配置:OTP_WD_DURATION[3:0],可以选择从1.0 ms到32768 ms的范围,默认为 1024ms。

审核编辑:刘清

NVIDIA RTX PRO 4500 Blackwell GPU测试分析