时间:2023-03-25 15:14

人气:

作者:admin

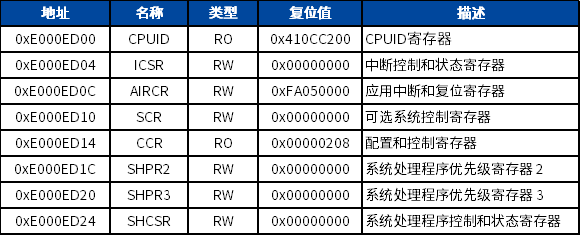

Cortex-M0系统控制块(SCB)是内核外设的主要模块之一,提供系统控制以及系统执行信息,包括配置,控制,上报系统异常等。

为了提高软件效率,CMSIS简化了SCB寄存器表示,在CMSIS中系统控制寄存器结构体:

typedefstruct

{__IMuint32_tCPUID;/*!< Offset: 0x000 (R/ ) CPUID Base Register */

__IOM uint32_t ICSR; /*!< Offset: 0x004 (R/W) Interrupt Control and State Register */

uint32_t RESERVED0;

__IOM uint32_t AIRCR; /*!< Offset: 0x00C (R/W) Application Interrupt and Reset Control Register */

__IOM uint32_t SCR; /*!< Offset: 0x010 (R/W) System Control Register */

__IOM uint32_t CCR; /*!< Offset:0x014 (R/W) Configuration Control Register */

uint32_t RESERVED1;

__IOM uint32_t SHP[2U];/*!< Offset: 0x01C (R/W) System Handlers Priority Registers. [0] is RESERVED */

__IOM uint32_t SHCSR; /*!< Offset: 0x024 (R/W) System Handler Control and State Register */

} SCB_Type;

一、CPUID

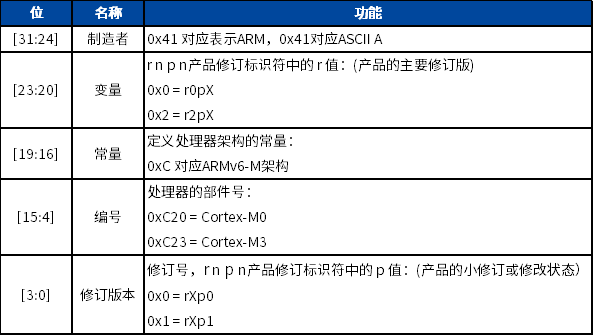

CPUID基地址寄存器包含处理器型号、版本等相关信息,是只读的,可以通过应用软件、调试器和烧录器等获取处理器的类型和版本信息。

Address: 0xE000ED00 Reset value: 0x410CC200

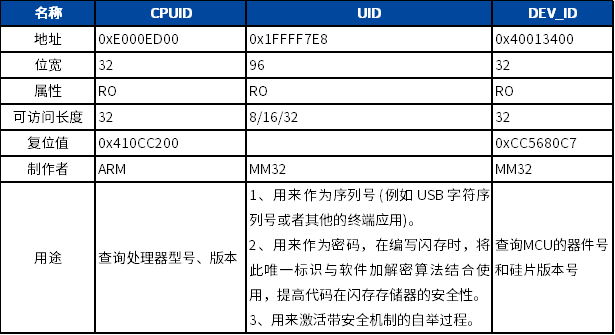

这个地方CPUID与我们经常提到的MCU的96位UID不同,CPUID是处理器的ID号,由Arm提供并实现,通过CPUID可以知道内核型号及版本等信息。

而96位UID是MCU产品ID,属于MM32,由上海灵动微电子股份有限公司提供并按照一定的规则实现,96位的产品唯一身份标识所提供的参考号码对任意一个系列微控制器,在任何情况下都是唯一的。

用户在何种情况下,都不能修改这个身份标识。

MCU还有一个DEV_ID编码,这个ID定义了MCU的器件号和硅片版本号,它是DBG_MCU的一个组成部分,并且映射到外部APB总线上。SW 调试口(2个引脚) 或通过用户代码都可以访问此编码。

DEV_ID地址:0x40013400 只支持32位访问,只读。

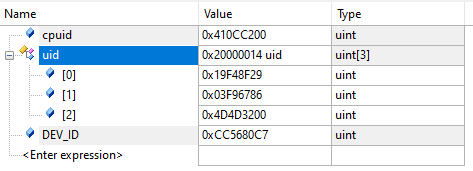

在CMSIS驱动库中,可以直接使用“ SCB->CPUID ” 获取处理器ID。读取MM32F0130的CPUID、UID和DEV_ID如下所示:

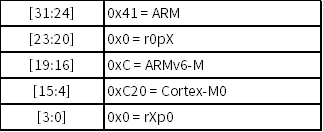

CPUID (0x410CC200)解析处理器信息:

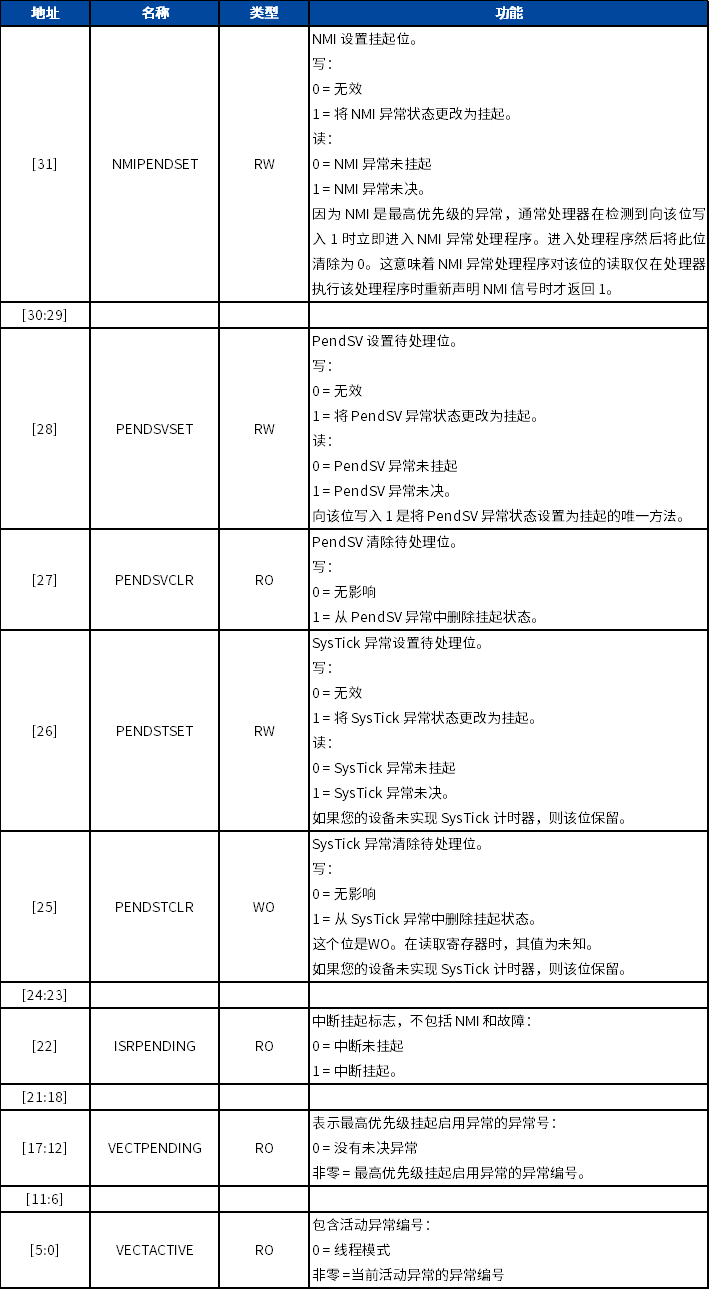

二、ICSR (Interrupt Control and State Register)

提供:

NMI异常的设置挂起位

为PendSV和SysTick异常设置挂起和清除挂起位

表示:

正在处理的异常的异常编号

是否有被抢占的活动异常

最高优先级未决异常的异常编号

是否有任何中断待处理

Address: 0xE000ED04 Reset value: 0x0000 0000

ICSR中的某些控制位仅供调试使用,大多数情况下,应用程序只会用ICSR来控制或者检查系统异常挂起状态。

PendSV(可挂起的系统调用)异常对 OS 操作非常重要,其优先级可以通过编程设置。可以通过将中断控制和壮态寄存器 ICSR 的 bit28挂起位置1来触发PendSV中断。与SVC异常不同,它是不精确的,因此它的挂起状态可在更高优先级异常处理内设置,且会在高优先级处理完成后执行。

利用该特性,若将PendSV设置为最低的异常优先级,可以让PendSV异常处理在所有其他中断处理完成后执行,这对于上下文切换非常有用,也是各种OS设计中的关键。在具有嵌入式OS的典型系统中,处理时间被划分为了多个时间片。

通过向中断控制和状态寄存器 ICSR 的 bit28 写入1挂起PendSV来启动PendSV中断,如果中断启用且有编写 PendSV 异常服务函数的话,则内核会响应 PendSV 异常,去执行PendSV 异常服务函数,这样就可以在PendSV中断服务函数中进行任务切换了。

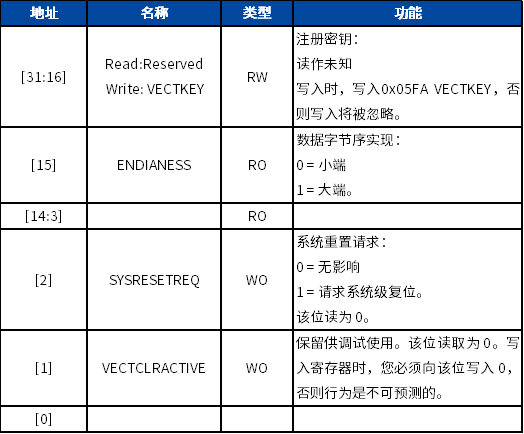

三、AIRCR (Application Interrupt and Reset Control Register)

AIRCR为数据访问和系统的复位控制提供字节序状态。

要写入该寄存器,您必须写入0x05FA VECTKEY 字段,否则处理器将忽略写入。

Address: 0xE000ED0C Reset value: 0xFA05 0000

任何对该寄存器的写操作,都必须将0x05FA写入到AIRCR[30:16],否则写操作将无效,若需要半字读取,需要写入0xFA05。

应用程序中系统执行软复位函数:

__STATIC_INLINEvoidNVIC_SystemReset(void)

{__DSB();//确保所有未完成的内存访问包括缓冲写入在重置之前完成

SCB->AIRCR=((0x5FAUL<< SCB_AIRCR_VECTKEY_Pos) |

SCB_AIRCR_SYSRESETREQ_Msk);

__DSB(); //确保完成内存访问

for(;;) /* wait until reset */

{

__NOP();

}

}

四、SCR (System Control Register)

SCR 控制进入和退出低功耗状态的特性。

Address: 0xE000ED10 Reset value: 0x0000 0000

审核编辑:刘清

NVIDIA RTX PRO 4500 Blackwell GPU测试分析