时间:2022-07-28 17:45

人气:

作者:admin

在大多数使用ARM处理器的系统中都会有很多应用或者任务同时运行,其中每个任务都在物理内存中拥有自己独立的页表。

每当应用程序启动时,操作系统都会为其分配一个页表,页表中的页表项将应用程序即将使用到的指令和数据映射到物理内存。如果应用程序映射到了未分配的物理空间,操作系统会完成相应页的分配,然后任务就可以进行下去。

多个任务可以同时运行,因为它们使用的是不同的VA-PA映射关系,而这些映射关系能够同时存在于物理内存中。当任务完成并且相应的页表映射不再需要时,该页表所处的物理空间可以被重新分配,删除相应的页表项(置成无效)并invalid TLB cache。

Address Space ID

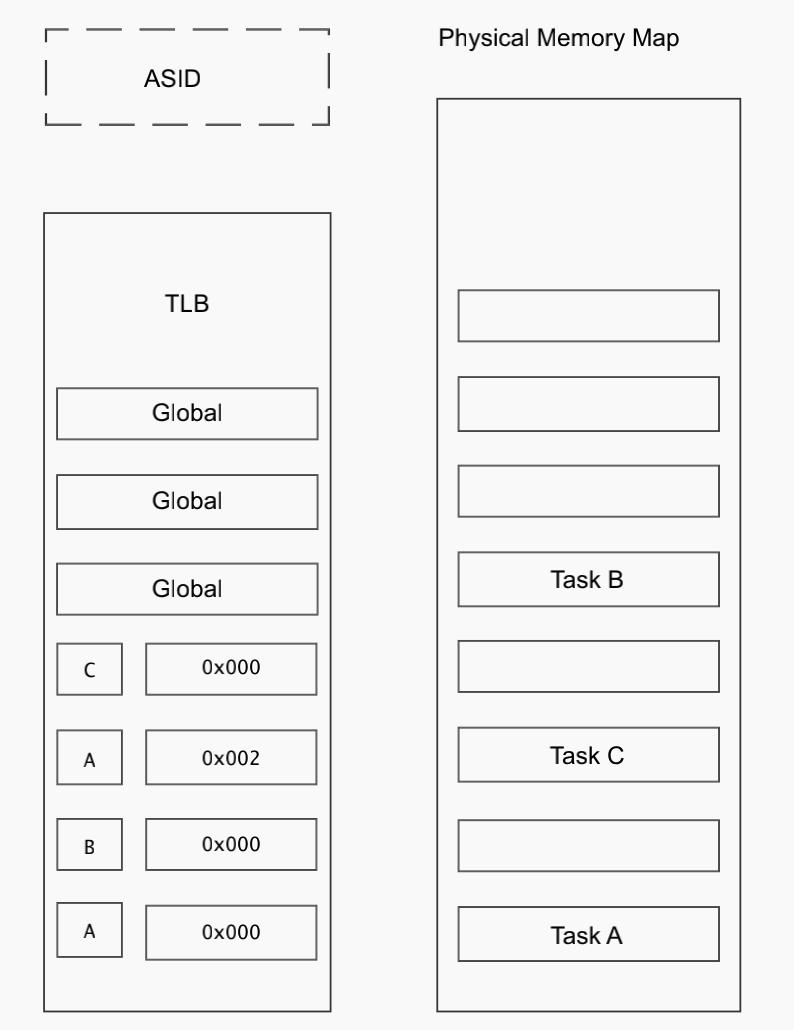

在页表中有一个nG(non-global)比特位。如果某个页设置了nG ,那么该页只与特定的应用或者任务相关联。当MMU执行VA-PA时,会同时用到VA和ASID(操作系统分配给每个任务的编号)。

作为页表内容的cache,TLB中的tag除了存储了VA,还有相应的ASID。在做TLB的hit-miss-check时,只有VA和ASID同时匹配才算hit。

上下文切换

所以,TLB中可能存放着多个相同VA对应的页表项。这些页表项具有不同的ASID,当某个ASID对应的任务完成或者这个任务的页表发生更改时只需要invalid某个ASID的TLB cache。这种操作叫context switches(上下文切换)。只针对特定ASID进行上下文切换,能够降低页表修改带来的性能开销,因为它避免了刷新全部的TLB。

审核编辑:刘清

上一篇:用C语言如何判断栈的增长方向呢

NVIDIA RTX PRO 4500 Blackwell GPU测试分析