时间:2022-02-25 09:18

人气:

作者:admin

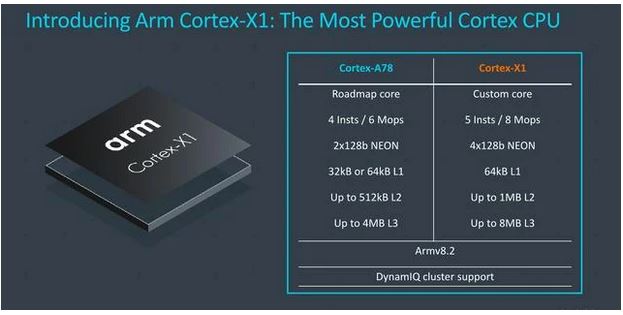

Arm全新的Cortex-X1高性能CPU,它是 Arm Cortex-X Custom 项目(CXC)的首款产品,仍属于Armv8家族。

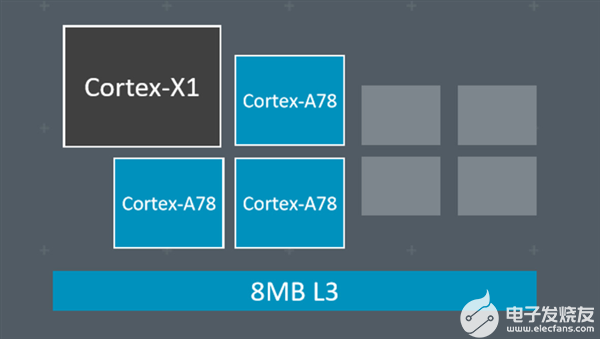

性能方面,根据官方给出的参考设计,采用一颗 X1 核心、三颗 A78 核心加四颗 A55 核心(共享 8MB L3 缓存)的设计相较前面提到的 A77 DynamiQ 方案(共享 4MB L3 缓存),能在占板面积仅增加 15% 的前提下,达成 30% 的峰值性能提升。

由于单Cortex-X1核心面积比A77和A78要大得多,所以不太可能采用原先的“4大 + 4小”设计,而是会按照Arm给出的“1超大 + 3大 + 4小”参考设计。Cortex-X1的L2缓存的最大容量为1MB,带宽是原来的两倍,可以最大限度地提高性能,而共享的L3缓存可以达到8MB,是前几代缓存的两倍。

与此同时,X1 的机器学习性能相较 A77 翻了一番,整数运算性能相比同代产品 A78 也有 22% 的提升。

WikiChip认为,Cortex-X1在结构设计上与Cortex-A78如出一辙,但几乎在每个地方都进行了扩展。前端解码部分从4端口增加到了5端口,宏指令缓存直接加倍,达到3000条,甚至超过Intel的Sunny Cove(2250条),但少于Zen 2(4000条)。乱序重排缓冲区(ROB)的大小也是扩充到224条,与Zen 2和Skylake持平。

执行部分中变化最大的是FP单元,也就是Arm特有的NEON浮点引擎,Cortex-X1上面直接将FP单元的数量倍增,达到4x128B的规模,宽度上基本等同于目前的桌面x86处理器,不过Arm目前的指令集并不允许单个长度大于128B的向量,在吞吐上肯定是不如桌面端处理器的。

初看之下,相对更追求极致性能的 X1 可能更像是一套为平板或是笔记本电脑准备的方案,而不像Cortex-A78一样完全用于智能手机。但是考虑到如今手游对高性能处理器的需求,感觉也是有厂商会把它用在手机上的,就像游戏型笔记本经常采用台式机CPU一个道理。

上一篇:MPU 2022及五年预测

NVIDIA RTX PRO 4500 Blackwell GPU测试分析