时间:2023-09-06 14:23

人气:

作者:admin

现在的市面上有着许许多多的自动布线软件可以选择,算法也愈发精准,在部分场合还是可以节省不少时间的。但是在对信号完整性要求极高的场合,自动布线的算法还是存在着许多缺陷,因此我们必须重视人工走线,每一根线都是经过工程师的深思熟虑,合理取舍得出来的结果,把它们看成是艺术的线条也不为过。下面我将继续通过图例的方式来和大家深度解读。

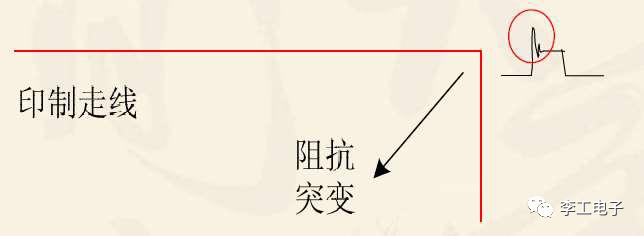

示例1

PCB板内不能出现直角走线,直角走线会导致线路的阻抗不连续,引起信号反射,产生振铃或过冲,形成强烈的EMI辐射。

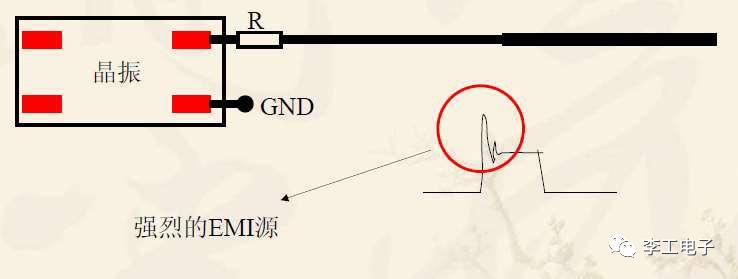

示例2

PCB走线时总线和时钟线的粗细应该保持一致,走线的粗细不均匀同样会导致线路阻抗不连续,进而引发EMI辐射。

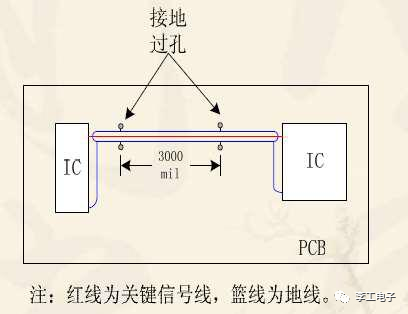

示例3

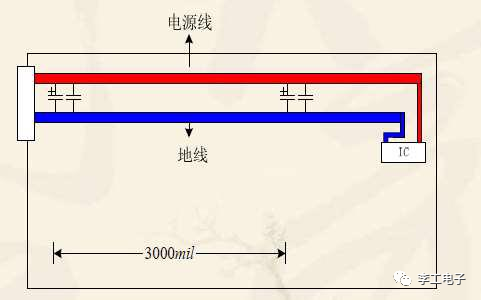

时钟线的两侧建议包地线,并且保证每隔3000mil接地一次,保证包地线上每个点的电位相等。

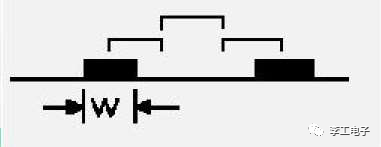

示例4

时钟线、总线和射频线等关键信号线与同层之间的平行走线应遵循3W原则,有关3W原则的介绍,可以翻看我之前写的一篇文章。总的来说应用3W的原则是为了避免同层之间不同信号的串扰。当然,3W原则只能保证70%的电场不互相干扰,要想保证98%的电场隔离度,就必须应用到10W的线中心距了。

此外,当电流≥1A的电源所用的贴片保险丝、磁珠、电感和钽电容等的焊盘应不少于两个过孔接到相对应的平面层,目的是为了减小过孔的等效阻抗。如果用到差分信号线,要求同层、等长、平行走线,保持阻抗一致,并且差分线之间没有其它走线,从而保证差分线间的共模阻抗相等,提高其抗干扰能力。

示例5

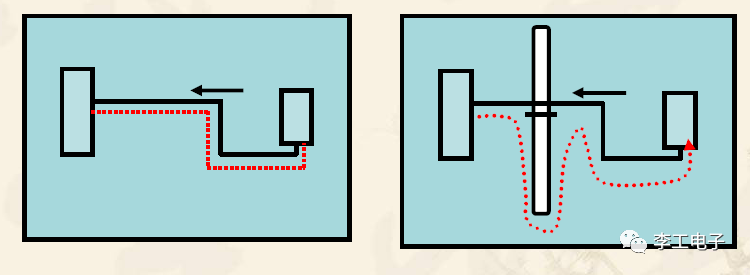

关键信号走线一定不能跨分割区(包括如过孔、焊盘导致的参考平面间隙),防止信号回路面积的增大。

示例6

单板上的滤波器(滤波电路)下方不要有其它无关信号的走线,避免形成的分布电容削弱滤波器的作用效果。

示例7

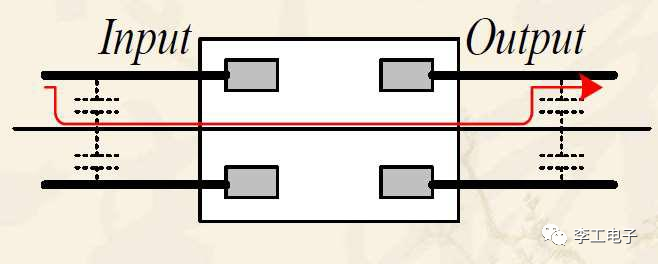

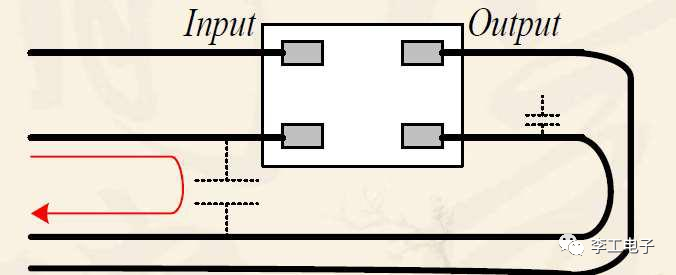

滤波器(滤波电路)的输入输出信号线不能相互平行、交叉走线,避免滤波前后的信号线直接耦合噪声。

示例8

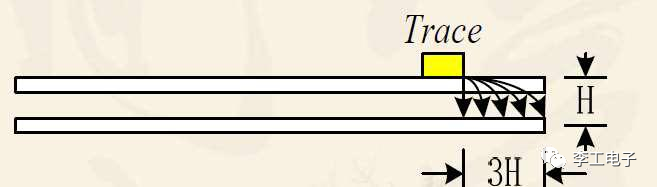

关键信号线距离参考平面边沿要求≥3H(之前的文章有详细介绍),为了抑制边缘辐射效应。

示例9

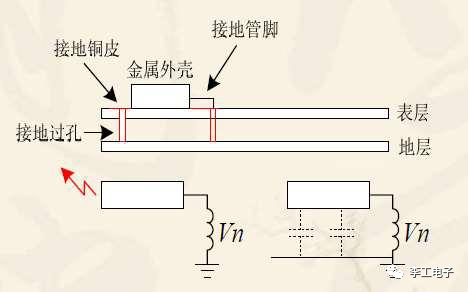

对于金属外壳接地的元件,应在其投影区的顶层敷上接地铜皮,通过金属外壳和接地铜皮间的分布电容来抑制对外辐射与提高抗扰度。

示例10

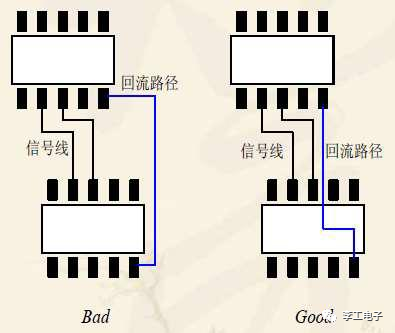

在单层板或双层板中,布线时应该时刻注意“回路面积最小化”的设计,因为信号回路面积越小,环路对外的辐射就越小,同时提高其抗干扰能力。

示例11

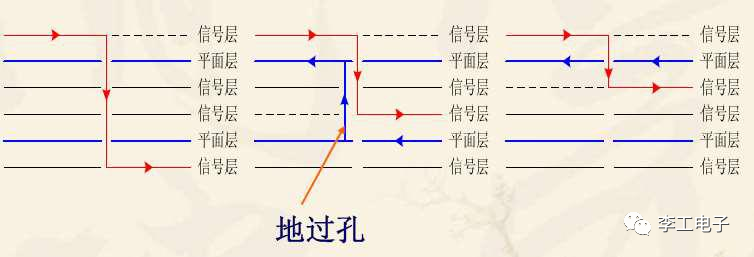

信号线(特别是关键信号线)换层时,应在其换层过孔附近设计过地孔,这样可以有效减小信号回路面积,减小辐射和增强抗扰度。

示例12

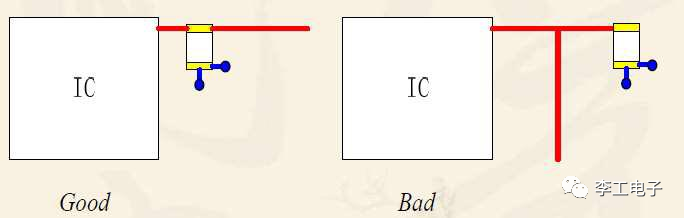

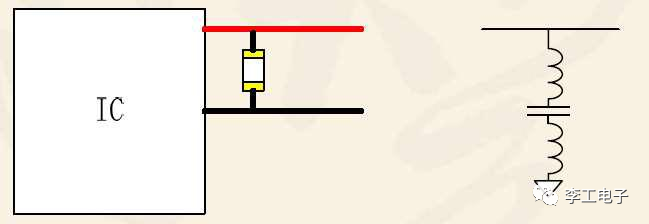

之前有讲过,滤波电容的应先经过滤波电容,再到器件管脚,使电源电流先经过滤波电容再给IC供电,并且IC反馈给电源的噪声也会被该滤波电容先滤掉,保证了电源的干净。

示例13

如果电源走线过长,应每隔3000mil对地加去耦电容,电容取值为10uF+1000pF,可以滤除电源线的噪声。

示例14

滤波电容的接地线和接电源线应该尽可能的粗、短,可以减小其串联电感,而等效串联电感会降低电容的谐振频率,削弱其高频滤波效果。

把以上的走线原则与传输线的理论相结合起来,即可设计出一块性能良好的高速PCB,其中一些细微参数的调整则需要大量的经验积累,不同的行业标准都有着自己的一套经验准则,但万变不离其宗,掌握好这些理论基础,将来无论去到哪个设计行业都能胜任。

上一篇:PCB工艺制程解析

下一篇:有关高速PCB布局设计的避坑指南