时间:2022-08-15 09:43

人气:

作者:admin

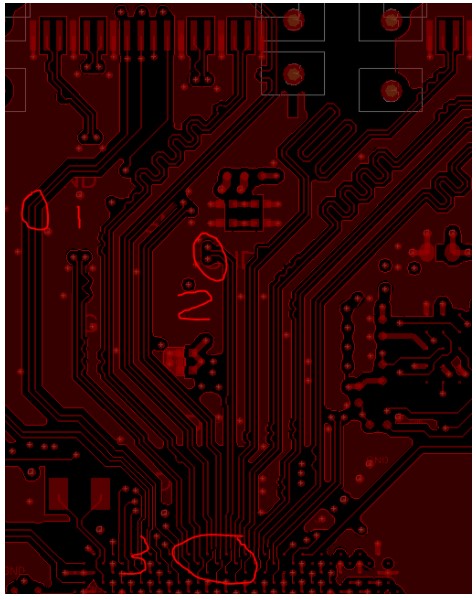

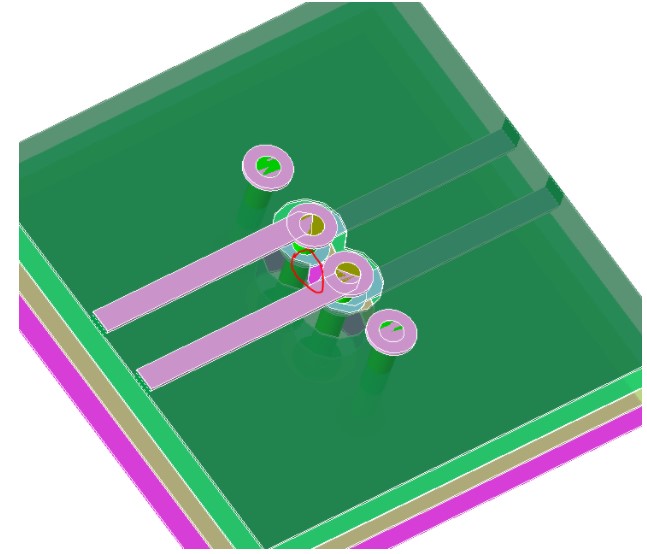

在日常PCB版图设计中,阻抗突变是不可避免的事情。下图为日常的版图走线:

图中标记处为常见的阻抗突变。

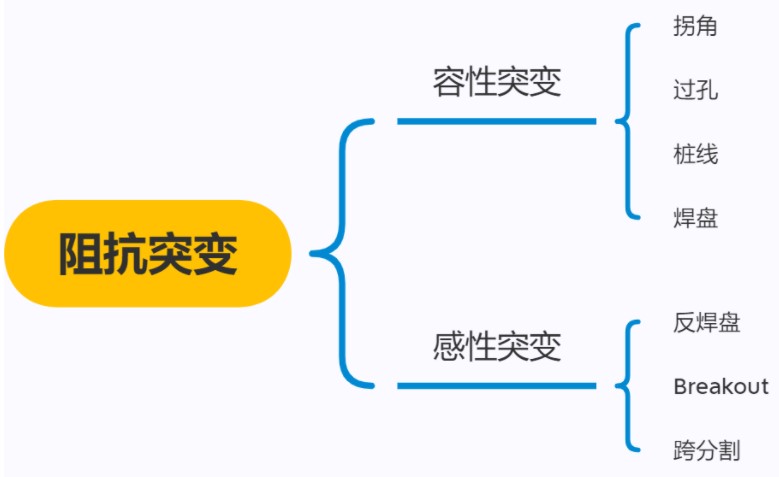

简短意赅,直接给出阻抗突变总结图:

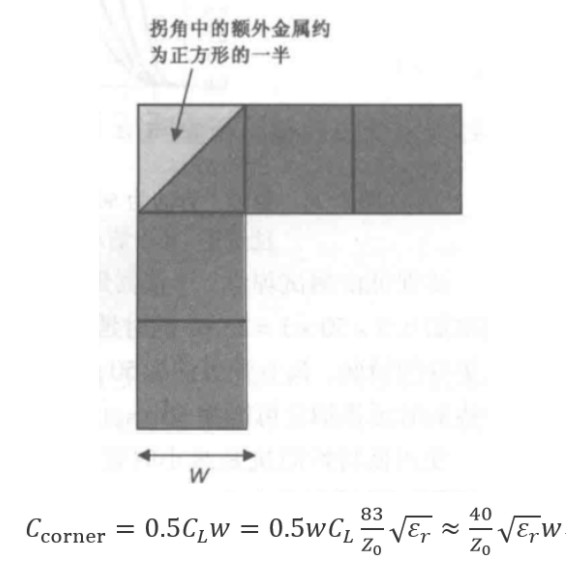

1、拐角

之前有推导过,导线中的电子速度为1cm/s, 所以90°拐角不会影响电子速度。90°拐角弯曲处更多影响是线宽,造成容性突变,影响信号质量。

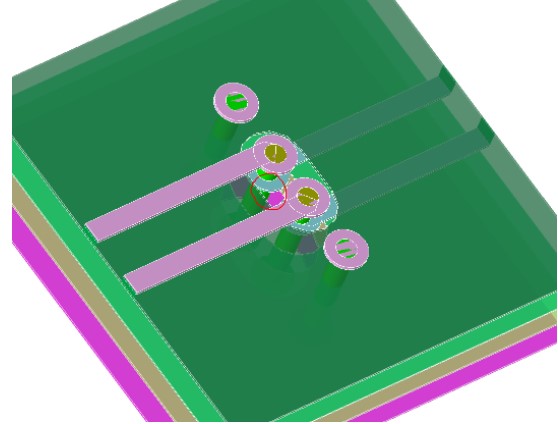

2、过孔

记得之前总结过孔经验法则的时候,有过这么两条:

1.50Ω传输线单位长度电容约为3.3 pF/in;

2.过孔桩线的单位长度电容约为5 pF/in。

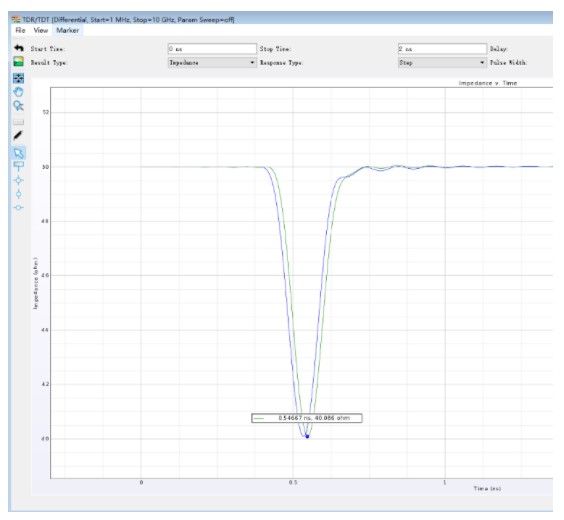

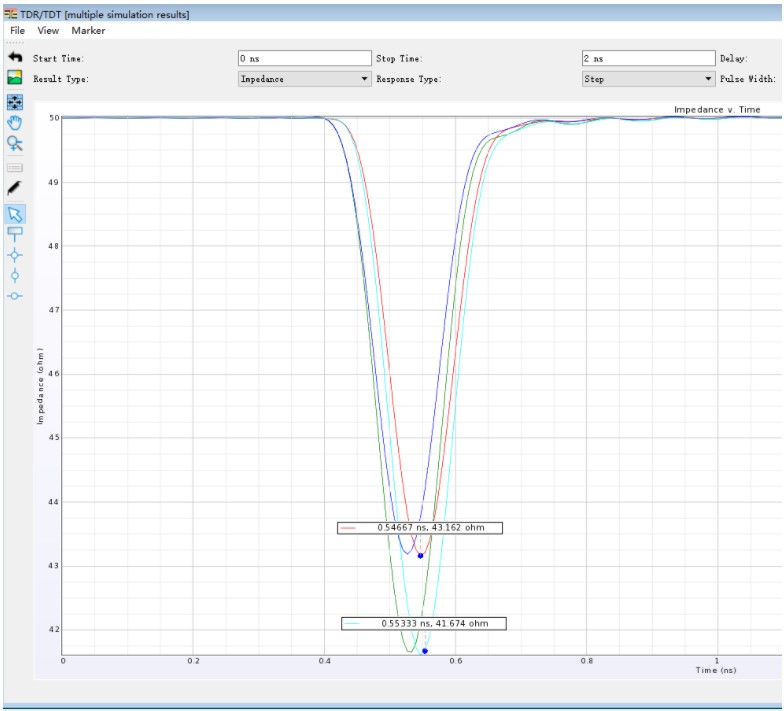

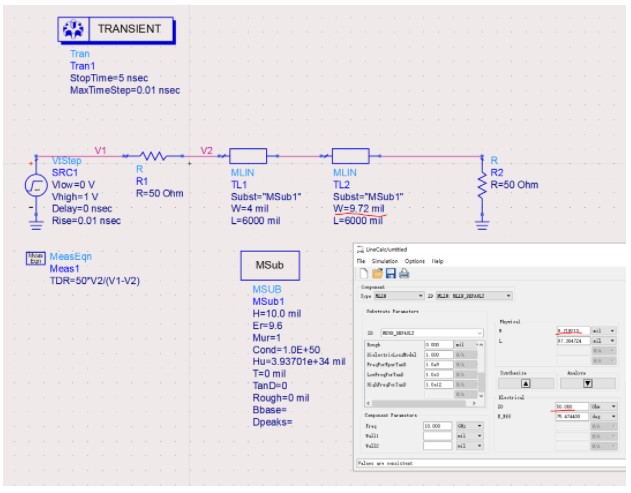

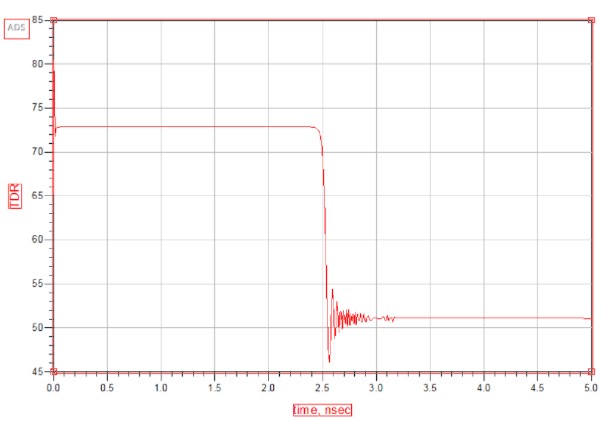

为了大家有个直观的印象,对过孔的阻抗突变做了个仿真,见下图:

在实际的工作中,所以才有对高速信号的过孔,进行优化处理,比如stiching Via,Antipad等来减少阻抗突变

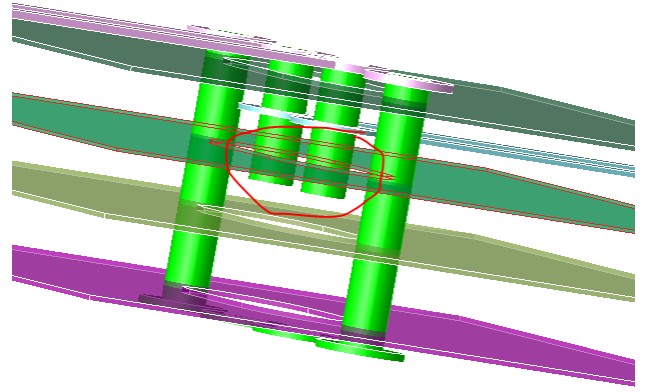

3、桩线

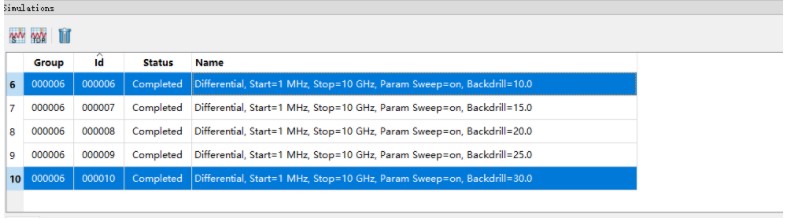

随着产品的高速化,很多Stub都做了Backdrill的处理,来控制反射,优化阻抗突变。这里面对高速率产品有需要考虑PCB工艺的误差。

桩线越长,阻抗的容性突变越大

4、Breakout

芯片出Pin的Breakout(Pin field)区域,一般走线比较窄,出了这个区域走线恢复正常。

Breakout 区域线变窄,阻抗变大。

5、其他

信号在走线部分跨分割,除了增加感性突变,还会引起串扰和辐射。这里就不做展开。

信号经过连接器从一块电路板传输到另一块电路板,连接器呈现出典型的感性负载特征。

6、影响

以上的这些突变会对信号产生什么影响呢?

容性突变使接收端产生下冲噪声&接收端信号延迟。

感性突变使接收端产生上冲噪声&接收端信号延迟。

7、总结

既然知道了阻抗突变的危害,我们就需要在实际的工作中,进行管控。之前的总结里给出过相关经验公式。

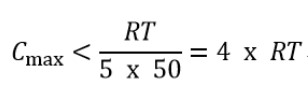

容性突变的裕量:

感性突变的裕量:

如果导线的特性阻抗为50Ω,信号上升边为1 ns,则可容许的最大串联电感约为0.2 x 50 x 1 ns=10 nH。

总之,管控也好,优化也罢,信号完整性工程师所要做的就是保证链路在裕量范围之内。

审核编辑:刘清