时间:2023-08-14 10:22

人气:

作者:admin

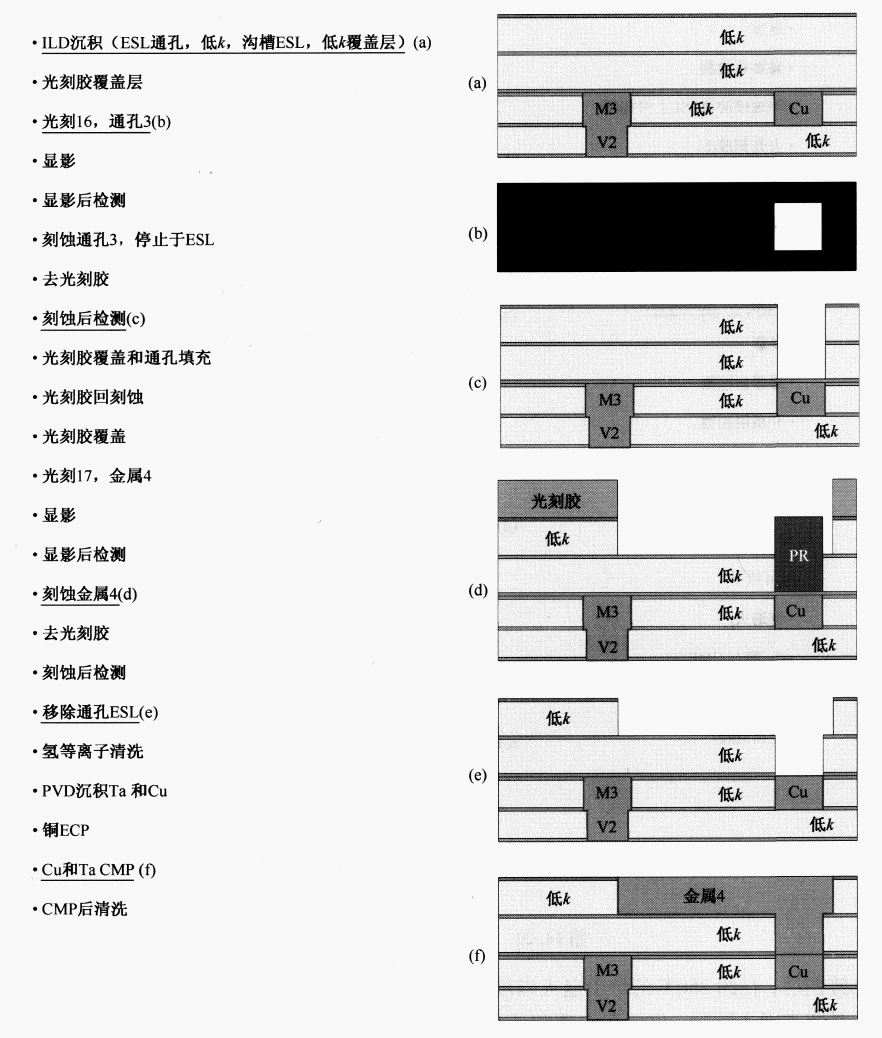

对于先通孔的过程,首先沉积通孔刻蚀停止层(ESL)的层间介质(ILD)、低k电介质、沟槽ESL、低k电介质的和覆盖层(下图(a))。

通孔ESL和沟槽ESL可以是氮化硅(SiN)或硅氮化碳(SiCN)。通过通孔光刻版(见下图(b))定义岀图形,通孔刻蚀即刻停止于通孔ESL(见下图(c))。

沟槽图形化前,晶圆表面覆盖一层光刻胶填充通孔并在刻蚀过程中保护通孔ESL(见下图(d))。

沟槽刻蚀后,通过光刻胶去除工艺移除通孔中的光刻胶。利用湿法清洗过程去除通孔底部的通孔ESL(见下图(e))。

Ta/CuPVD和铜ECPX艺后,利用金属CMP工艺从晶圆表面去除铜和铤,并完成双镶嵌铜金属化过程。

氯溅射刻蚀过程中的重离子轰击有时可以从通孔底部溅射岀少量的铜并沉积在通孔侧壁上。

对于大多数电介质,如硅酸盐玻璃和多孔二氧化硅,铜原子扩散非常快。

如果铜原子扩散到硅衬底,将可能导致微电子器件性能不稳定。因此,金属PVD前的氯溅射刻蚀可能会导致IC芯片长期的可靠性问题。

氢等离子体清洁工艺使用等离子体产生氢自由基,自由基和氧化铜发生反应生成铜和水蒸气,从而可以在没有离子轰击的情况下,有效地去除通孔底部的原生氧化铜。

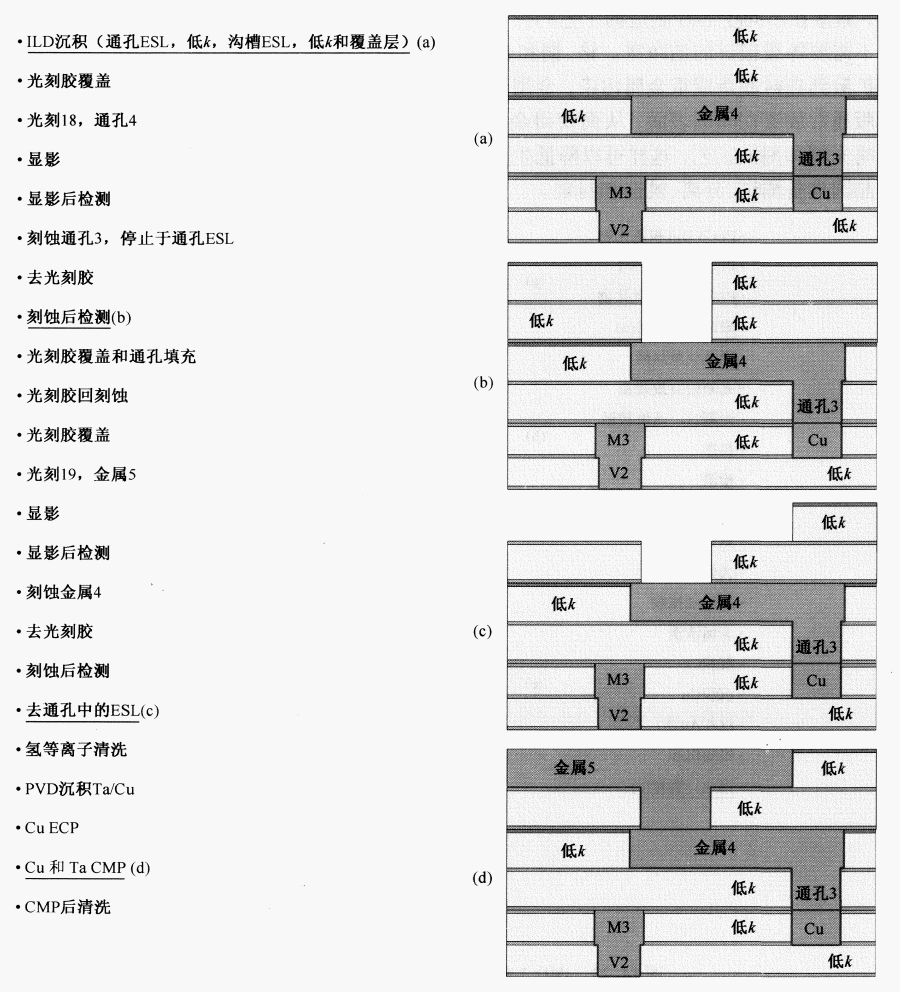

如下图所示为先通孔铜互连工艺流程。

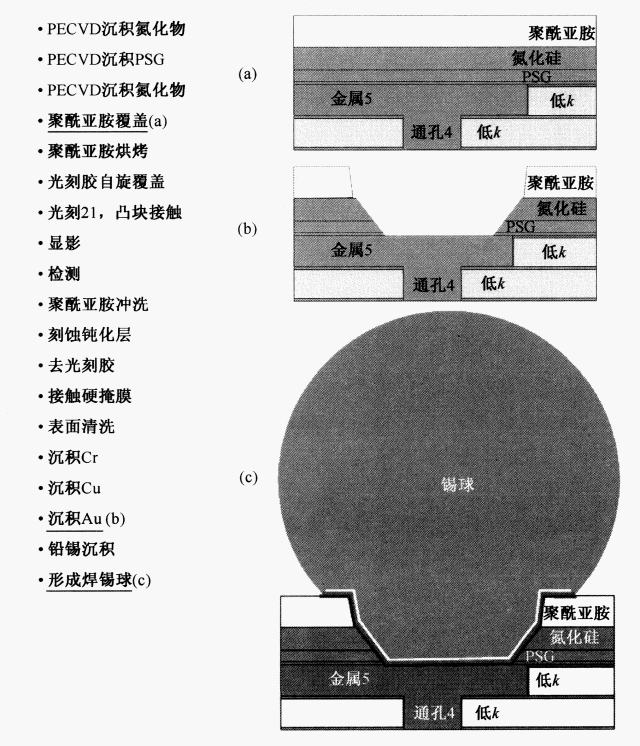

下图显示了最后的金属层和钝化过程。氮化硅是一种非常致密的材料,可以防止水和钠等杂质扩散进入芯片导致器件损坏。

通常使用塑料封装芯片作为钝化介质保护芯片免受化学污染,以及晶粒测试、分离和封装过程中的机械损伤。厚的钝化氮化物沉积之前,沉积一层PSG氧化层以提供应力缓冲。

对于采用陶瓷封装的芯片,效果比塑料封装更好但价格昂贵,CVD二氧化硅或氮氧化硅层是常用的钝化电介质。钝化层沉积后,覆盖一层聚酰亚胺,随后涂敷光刻胶,然后烘烤并显影。

聚酰亚胺在光刻胶显影过程中被刻蚀。聚酰亚胺涂层可以保护晶圆在传送过程中免受机械划伤,而且还可以保护微电子器件免受背景辐射,如阿尔法辐射。光刻胶去除后,晶圆加工过程基本完成。

下图(c)显示了倒装芯片封装的凸点形成工艺。凸点形成工艺是晶圆加工工艺的最后阶段,通常在不同于芯片制造的工艺间操作,这是因为凸点的尺寸非常大,约50~100um,所以并不需要等级很好的洁净室。

铬、铜和金作为衬垫用于实现低接触电阻,铬用于防止铜、金和铅扩散到硅衬底造成重金属污染,金用于帮助在晶圆表面形成铅锡合金。

金属沉积过程中,光刻版通常放置在晶圆表面,从而使得金属只沉积在凸点开口处。

使用图形化的金属沉积可以省略光刻和刻蚀工艺,这样可以降低生产成本。铅锡合金再流动后,在晶圆表面形成凸点,然后晶圆准备测试、分离、挑选和封装。

审核编辑:刘清

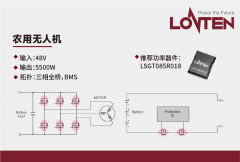

龙腾半导体SGT MOSFET LSGT085R018在智慧农业无