时间:2023-09-28 14:09

人气:

作者:admin

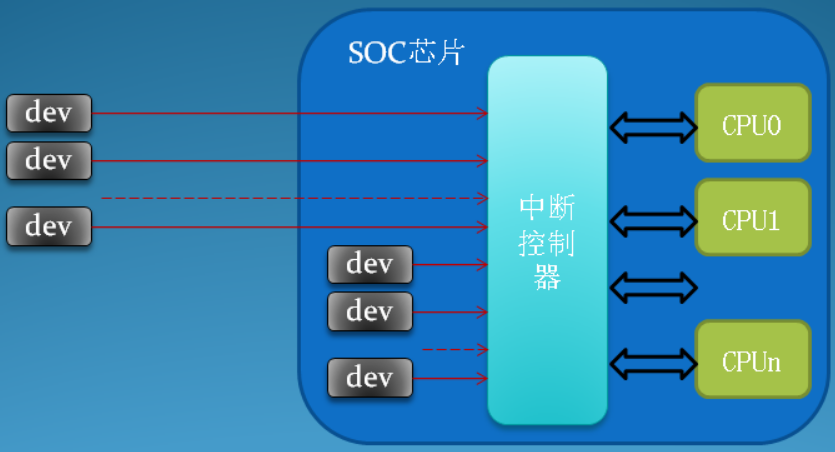

中断子系统硬件架构

一个完整的设备中,与中断相关的硬件可以划分为3类,它们分别是:设备、中断控制器和CPU本身。

设备:设备是发起中断的源,当设备需要请求某种服务的时候,它会发起一个硬件中断信号,通常,该信号会连接至中断控制器,由中断控制器做进一步的处理。在现代的移动设备中,发起中断的设备可以位于soc(system-on-chip)芯片的外部,也可以位于芯片的内部,因为目前大多数soc 都集成了大量的硬件 IP,例如 I2C、SPI、Display Controller 等等,就是内部中断源。

中断控制器:中断控制器负责收集所有中断源发起的中断,现有的中断控制器几乎都是可编程的,通过对中断控制器的编程,我们可以控制每个中断源的优先级、中断的电气类型,还可以打开和关闭某一个中断源,在smp系统中,甚至可以控制某个中断源发往哪一个CPU 进行处理。对于 ARM 架构的 soc,使用较多的中断控制器是VIC(Vector Interrupt Controller),进入多核时代以后,GIC(General Interrupt Controller)的应用也开始逐渐变多。STM32单片机的中断控制器叫 NVIC,ARM架构的中断控制器一般为GIC,不同架构有不同的中断控制器。

CPU:最终响应中断的部件,它通过对可编程中断控制器的编程操作,控制和管理者系统中的每个中断,当中断控制器最终判定一个中断可以被处理时,他会根据事先的设定,通知其中一个或者是某几个

cpu 对该中断进行处理,虽然中断控制器可以同时通知数个 cpu 对某一个中断进行处理,实际上,最后只会有一个 cpu 相应这个中断请求,但具体是哪个 cpu进行响应是可能是随机的,中断控制器在硬件上对这一特性进行了保证,不过这也依赖于操作系统对中断系统的软件实现。

为什么需要中断控制器?

CPU 要做的事情主要是运算。一个 CPU 有很多个中断可以使用,他们之间也有优先级。由于中断过多,我们需要中断进入 CPU处理之前,先进入中断控制器,让中断控制器来控制中断的优先级、触发方式、enable 和 disable等,为CPU减轻负担,让CPU专注于运算。

上一篇:Linux系统为什么需要中断

下一篇:中断控制器级联的类型有哪几种