时间:2023-07-07 14:17

人气:

作者:admin

今天我们要介绍的时序分析基本概念是 wire load model . 中文名称是线负载模型。是综合阶段用于估算互连线电阻电容的模型。

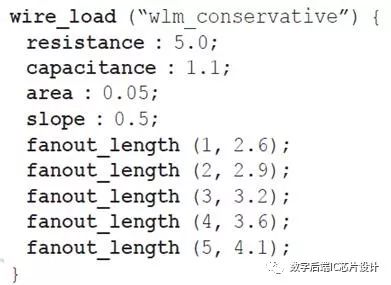

下图就是一个比较常见的wire load model。该模型包含了互连线长度,电阻,电容,面积等信息。在综合阶段计算时序时,工具从lib文件中得到cell的延迟,而互连线的延迟则从线负载模型中的计算出来的RC信息得到。

怎么估算呢?我们来看上面这个例子,首先,我们通过线负载模型得到互连线的长度:假如我们需要知道一根扇出是6互连线的RC信息。

首先我们得知道互连线的长度,根据fanout_lenth的查找表:

互连线的长度 = 扇出5对应的互连线长度+(6-5)×slope(斜率)=4.1+0.5= 4.6

互连线电阻 = 互联线长度 x 互联线单位电阻值=4.6×5.0=23

互连线电容 = 互联线长度 x 互联线单位电容值=4.6×1.1=5.06

使用方法:

采用工艺库lib1800中的wlm_conservative wire load model模型

set_wire_load_model -library lib1800 -name wlm_conservative

下一篇:CMOS施密特触发器仿真设计