时间:2023-09-21 18:24

人气:

作者:admin

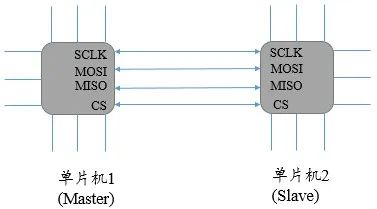

串行外围设备接口(Serial Peripheral Interface,SPI)是一种高速、全双工、同步通信总线,常用于单片机和E2PROM、FLASH、实时时钟、数字信号处理器等器件之间的通信,它主要是主从方式通信,通常只有一个主机和多个从机。

标准SPI协议有4根线,SCLK(必须存在),其他三条线(MOSI、MISO、CS)都可以根据实际情况进行删减。

SCLK:时钟信号,由主机产生( 必须存在)

MOSI:主机给从机发送指令或数据的通道

MISO:主机读取从机的状态或数据的通道

CS:从机片选使能信号

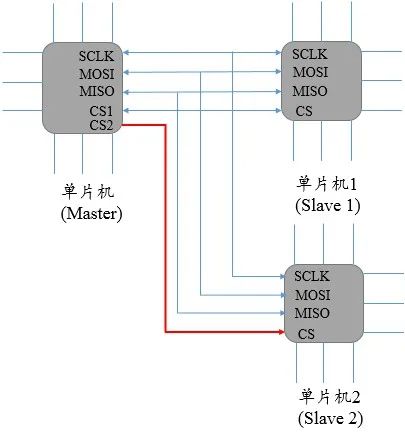

在同一时刻,主机只能跟一个从机进行通信。当总线上存在多个从机时,需要进行片选将从机的CS接口电平拉高或拉低。

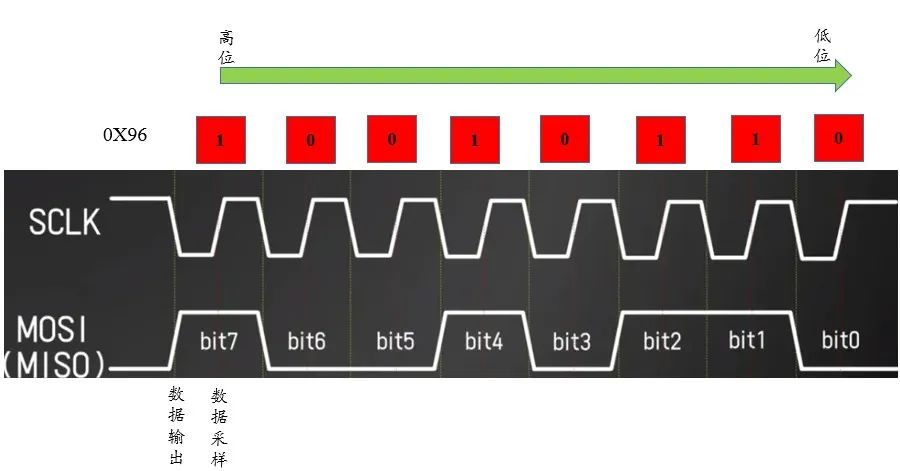

SPI协议和I2C协议一样,数据是从高位到低位依次发送,SPI协议中SCLK在空闲时可以是高电平也可以是低电平。下面以空闲时,SCLK为高电平举例。

当SCLK出现下降沿即从高电平跳到低电平时,进行数据输出;当SCLK出现上升沿即从低电平跳到高电平时,进行数据采样 。

SPI总线寻址模式

和I2C协议相比,SPI协议没有开始位、停止位、应答位,规则上简单很多。SPI协议中SCLK在空闲时可以是高电平也可以是低电平,这其实反映了时钟的极性。 上图中,CPOL=1,CPHA=1 。

CPOL时钟极性:

CPOL=0,SCLK空闲时状态为低电平

CPOL=1,SCLK空闲时状态为高电平

时钟的相位:它决定了什么时候进行数据输出,什么时候进行数据采样。

CPHA时钟相位:

CPHA=0,每个周期的第一个跳变沿进行数据采样

CPHA=1,每个周期的第一个跳变沿进行数据输出

从profibusDP转ModbusTCP,一网打尽转换技巧!