时间:2023-09-28 11:27

人气:

作者:admin

1.概述

信号完整性(Signal Integrity,SI)是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传输到接收端,我们就称该信号是完整的。信号完整性分析的目的就是用最小的成本,最快的时间使产品达到波形完整性、时序完整性、电源完整性的要求。

2.典型的信号完整性问题

信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值,差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同引起的。主要的信号完整性问题包括反射、振荡、地弹、串扰、时序等。其中反射和串扰是引发信号完整性问题的两大主要因素。

2.1 反射

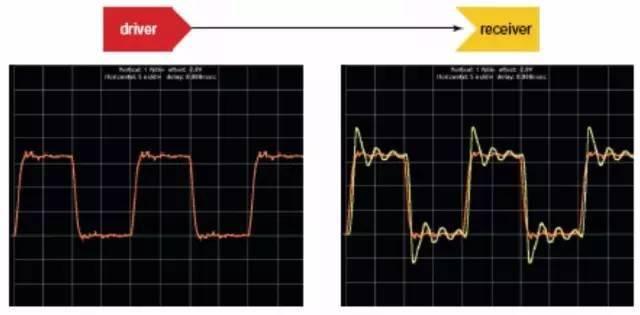

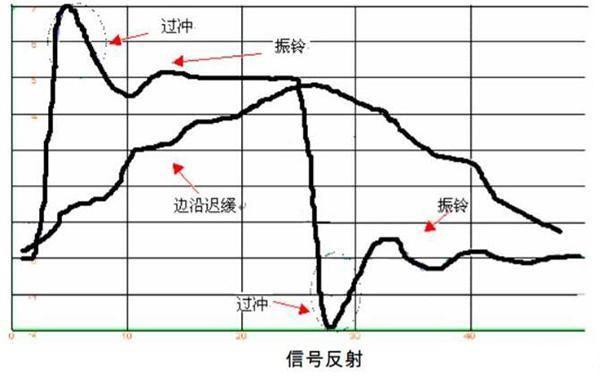

反射是指信号在传输线上的回波现象,由于传输系统阻抗不匹配,会使传输的信号不能被完全吸收,造成部分能量返回。反射造成信号出现过冲(Overshoot)、振铃(Ringing)、边沿迟缓(阶梯电压波)。过冲是振铃的欠阻尼状态,边沿迟缓是振铃的过阻尼状态。下图为信号反射的三种表现形式。

过冲一方面会造成强烈的电磁干扰,另一方面会损伤后面电路的输入级,甚至失效。而振铃会带来信号长时间不能稳定,边沿迟缓带来信号上升时间过长,二者都可能带来信号的时序问题,如时钟数据同步、建立与保持时间不满足等。

2.2串扰

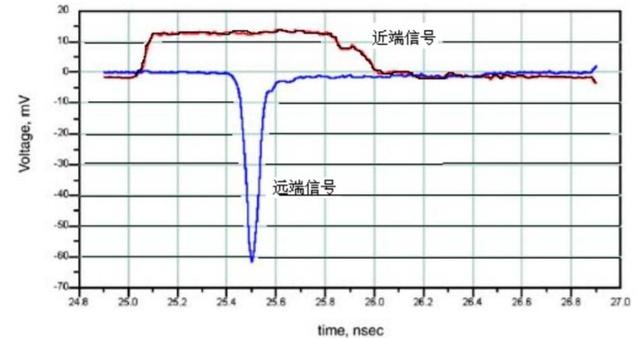

由于导线之间间距过小,当有快速变化的电流流过导线时会产生交变的磁场,而使邻近的导线上感应出信号电压,称为串扰(Crosstalk)。下图为受影响信号线上的串扰信号。

串扰干扰着正常的信号流,有可能造成数据错误,是造成误码的主要原因之一。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及信号线的端接方式对串扰都有一定影响。

3.信号完整性产生原因

常见的信号完整性问题引起问题的原因和相应的解决方法:

4.信号完整性设计的难点

SI设计的主要难点在于需要综合信号幅度、噪声、边沿、延时等影响信号质量的多种因素,并且这种因素常常相互依赖,互相影响,交叉在一起,这就导致抑制了某一方面的影响可能又导致其他方面的影响恶化,因此SI设计中往往需要对各种因素反复权衡,做出系统化的综合设计。

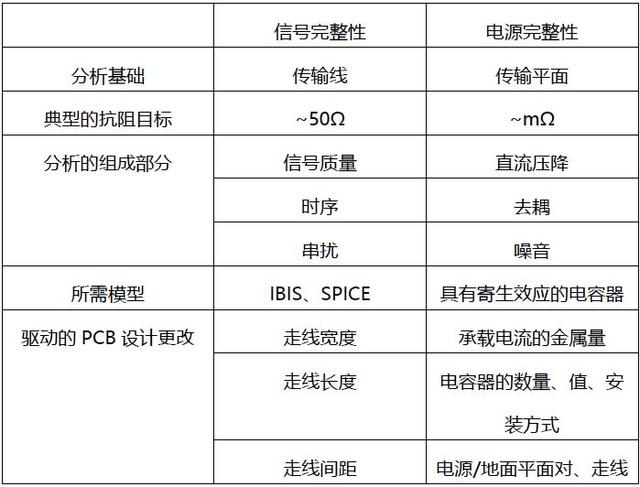

5.信号完整性和电源完整性之间的差异

在信号完整性中,重点是确保传输的逻辑1在接收器中看起来就像 1(对0同样如此)。在电源完整性中,重点是确保为驱动器和接收器提供足够的电流以发送和接收1和0。因此,电源完整性可能会被认为是信号完整性的一个组成部分。实际上,它们都是关于数字电路正确模拟操作的分析。

从profibusDP转ModbusTCP,一网打尽转换技巧!