时间:2023-09-08 09:09

人气:

作者:admin

LWIP 是使用裸机设计以太网的良好起点,在此基础上我们可以轻松调整软件应用程序以提供更详细的应用程序。LWIP Echo 服务器的使用首先使我们能够确定底层硬件设计是否正确。

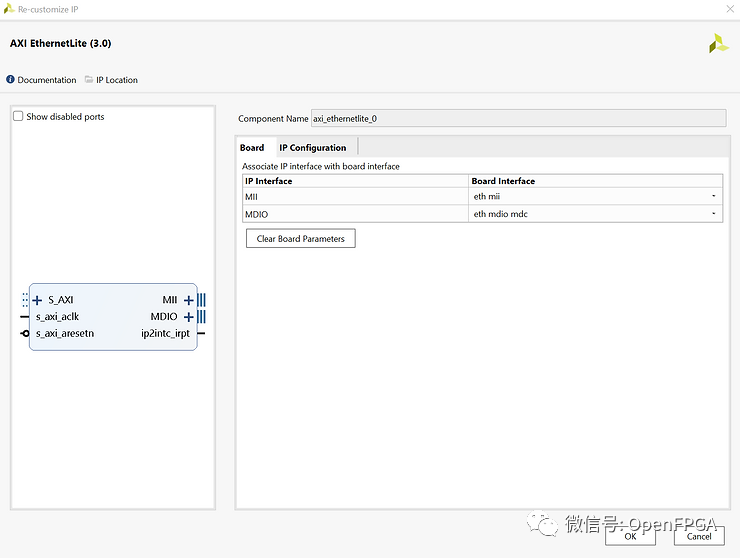

此设计的核心是 Vivado IP 中的 AXI Ethernet Lite IP 模块(我在该项目中使用Vivado 2023.1)。AXI Ethernet Lite IP 适用于 10 或 100 Mbps 以太网链路。这提供了一个资源很少的以太网接口,对于我们低成本的设备(例如 Artix 7 FPGA)来说是理想的选择。通过简单的以太网接口,设计人员可以使用以太网对最终应用进行命令和控制。

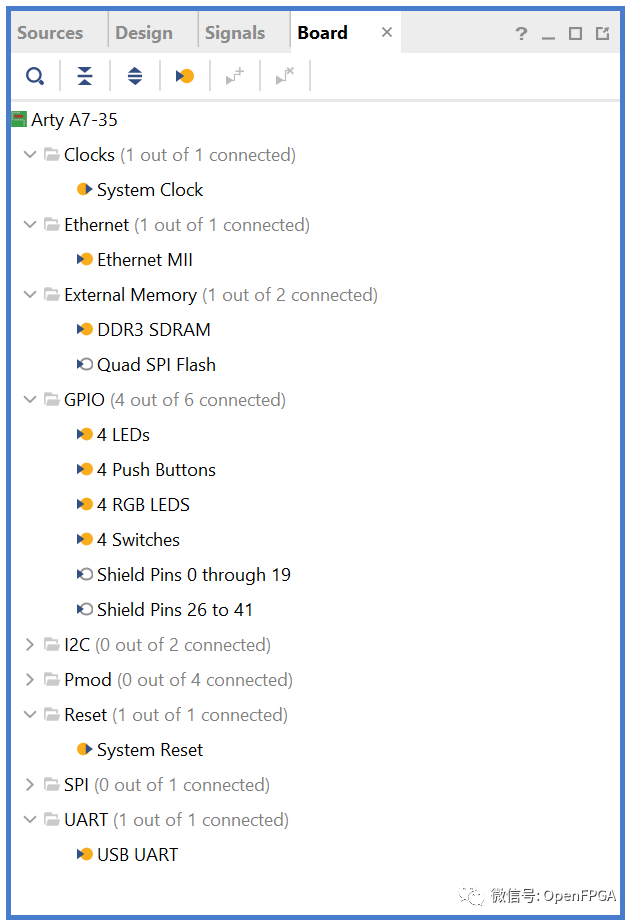

为了验证这一IP,将使用 Arty A7-35T 板。创建项目后,创建框图,从 IP Designer 的 Board 选项卡添加以下 IP

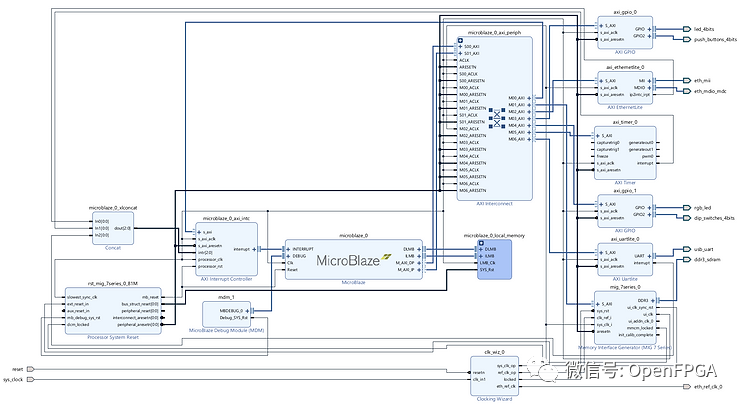

可以使用 Git Repo 中存储的 TCL 脚本重新创建完整的设计。关键设计点包括使用 DDR 时钟输出为除 AXI Ethernet Lite IP 模块(时钟频率为 100 MHz)之外的所有 AXI 网络提供时钟。

DDR 的系统时钟频率为 100 MHz,参考时钟频率为 200 MHz。DDR 接口运行频率为 324.99 MHz,其接口频率为大多数 AXI 接口频率的 1/4 (81.2475MHz)。

除了 AXI Ethernet Lite IP 之外,我们还需要提供 25MHz 参考时钟来配置以太网 Phy。

Vivado 中的设计如下所示。

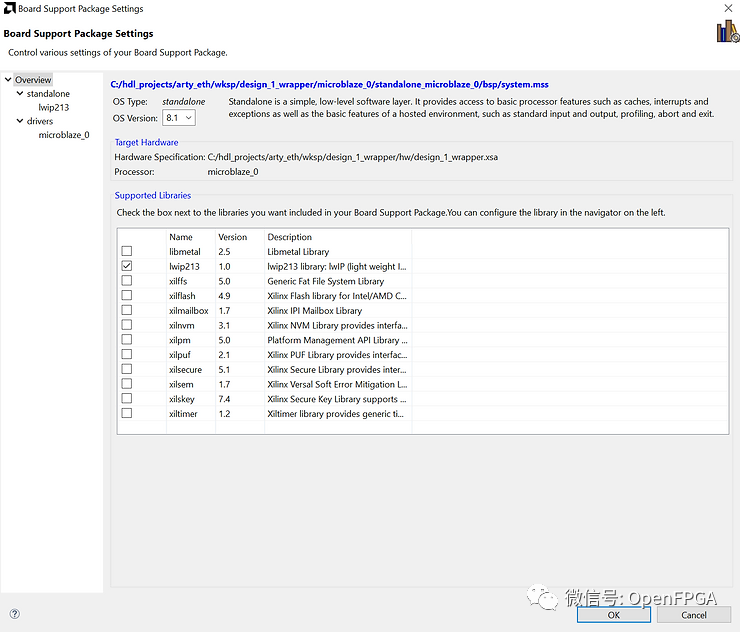

有了可用的比特流,从 Vivado 导出XSA,并为 Vitis 中新应用项目导入XSA。

以 MicroBlaze 处理器为目标并选择 LWIP Echo Server 应用程序。

创建项目后,可以构建应用程序和平台。请注意,在 Vitis 2023.1 中编译 LWIP 时,xadaptor.c 文件中存在错误,第 388 行有两个状态声明,分别为 16 位和 32 位变量。如果发生这种情况,请注释掉 16 位声明并重新编译设计。

将 Arty A7 板通过网线连接到 PC 后,可以在 Arty A7 板上下载并运行应用程序。

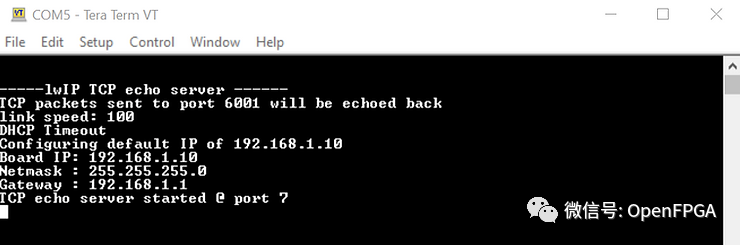

终端将输出 IP 地址并提供发送到端口 7 的所有命令。

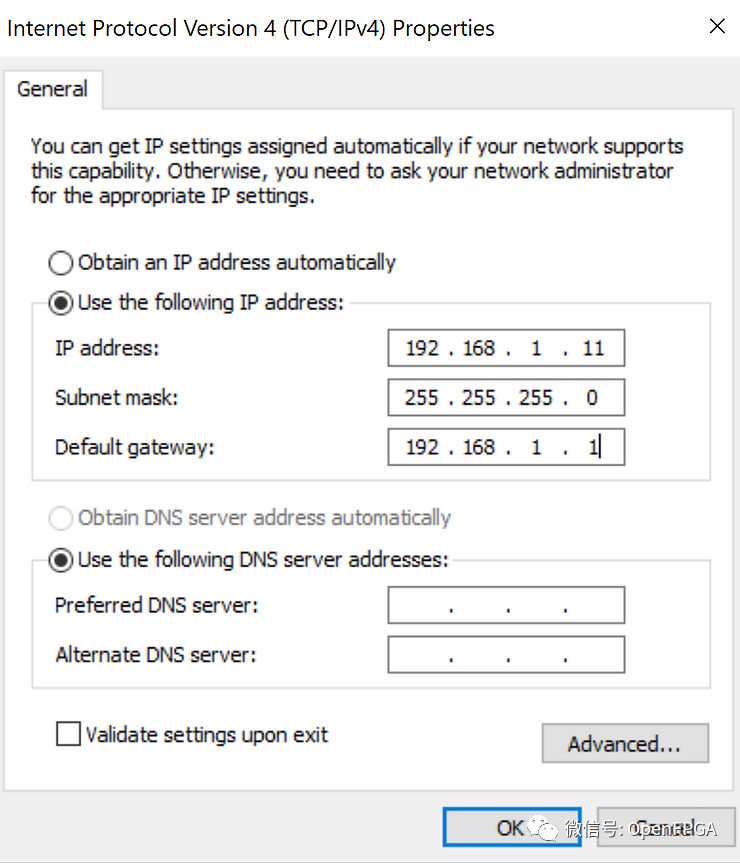

为了能够通过 Telnet 连接到 Arty A7,我们需要首先将主机的 IP 地址配置为与 Arty A7 类似。

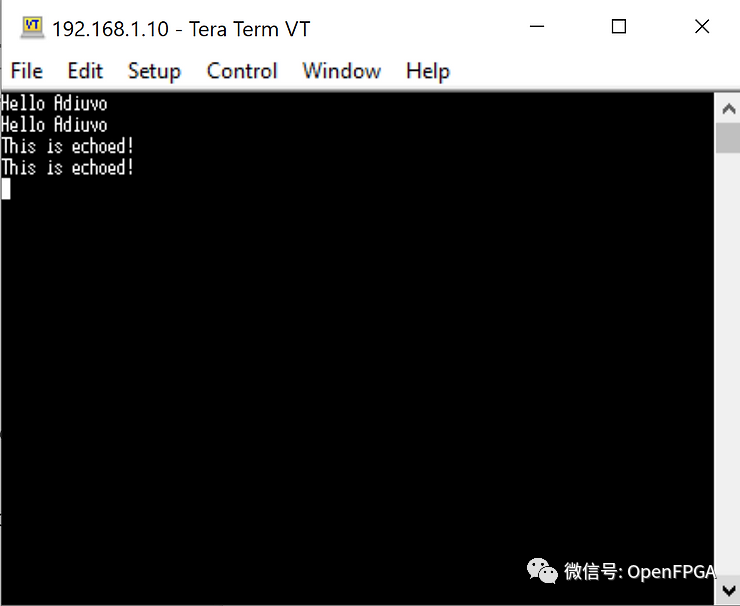

主机上的 IP 设置正确后,我们可以打开与 Arty Board 的 Telnet 会话并发送要回显的命令。

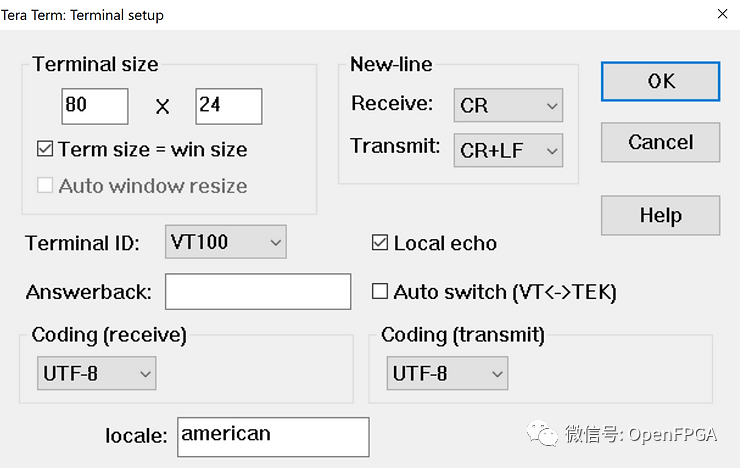

最好将终端程序设置为执行本地回显并将 CR/LF 附加到消息中。

然后我们可以输入文本并观看它的回显。

今天的历程差不多就这样,这为我们开发以太网应用提供了一个良好的起点,后续我们就可以开发新的以太网项目。

审核编辑:刘清

上一篇:螺母生产流程以及优化措施

下一篇:各种常见接口类型及其区别

从profibusDP转ModbusTCP,一网打尽转换技巧!