时间:2023-07-22 16:19

人气:

作者:admin

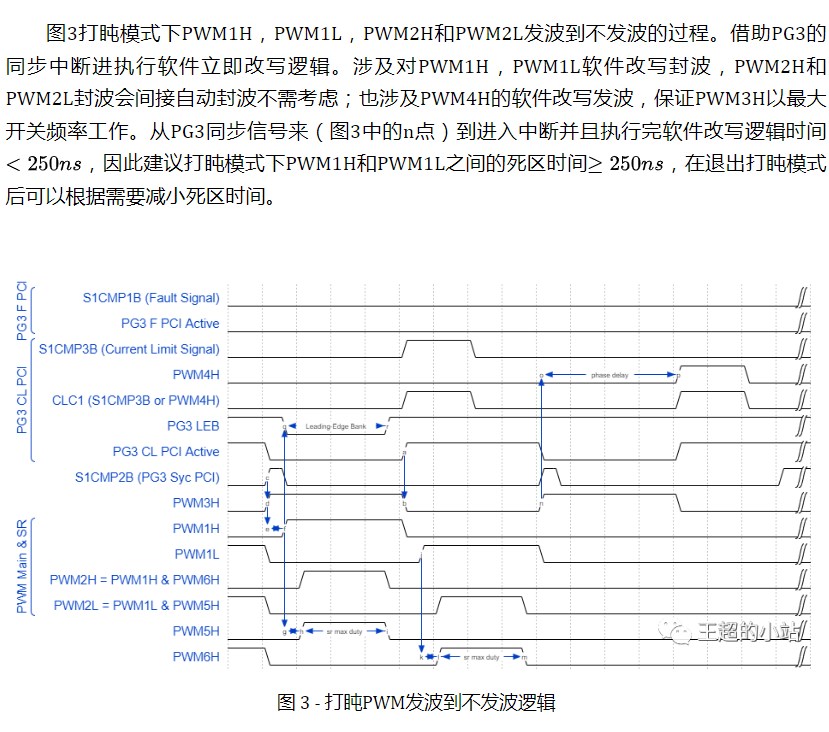

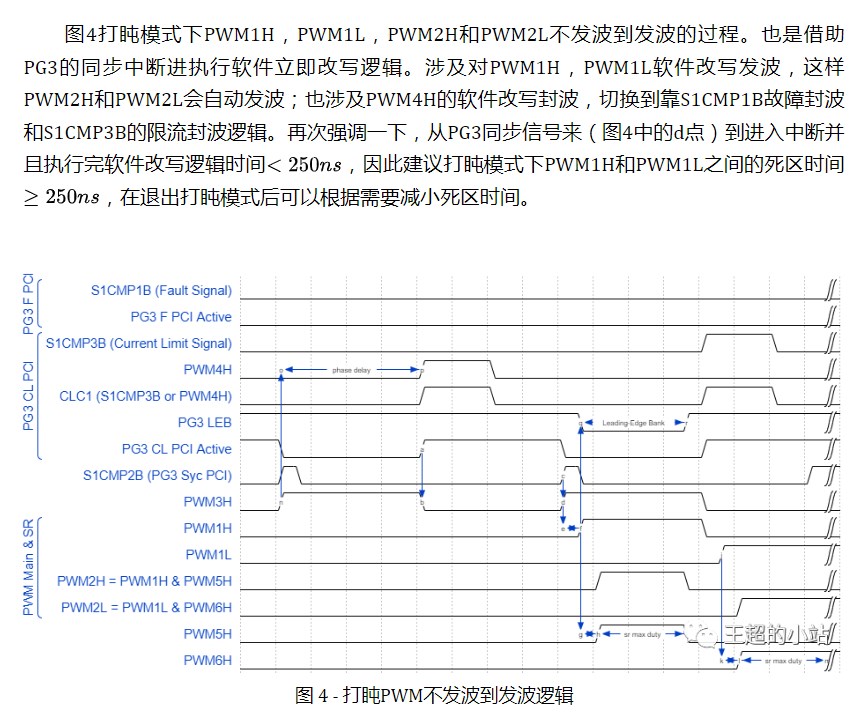

本文介绍基于 dsPIC33CH512MP508 实现的LLC峰值电流控制PWM发波逻辑,该发波逻辑充分利用了 dsPIC33C 系列MCU强大的PWM外设,用到了诸如PCI同步功能,PCI故障、限流对输出的硬件改写,借助软件改写实现Burst模式下发波与否,以及不同组PWM之间的组合逻辑。

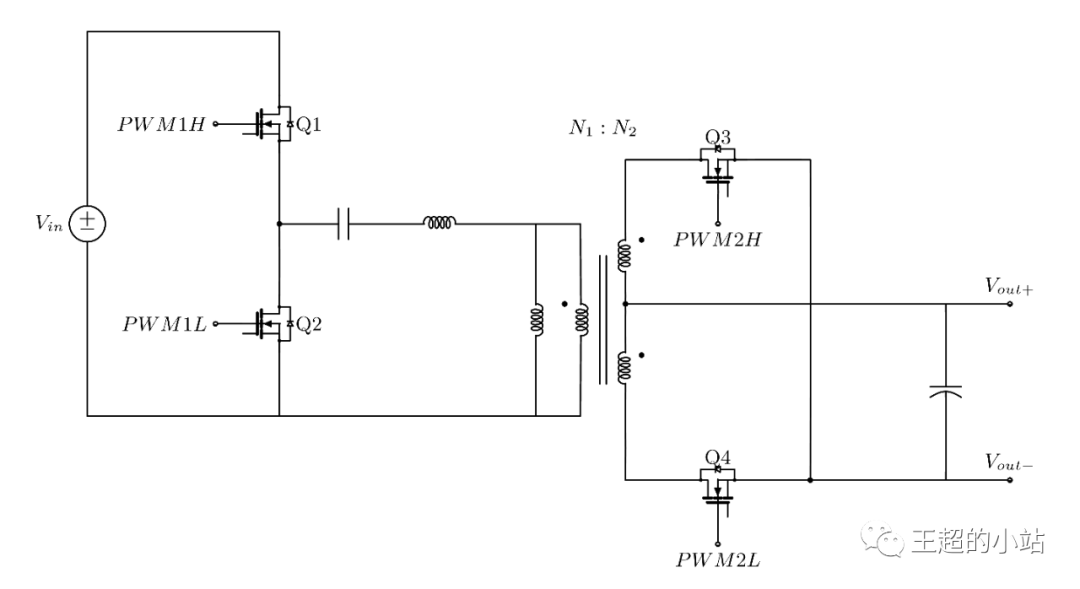

带同步整流的半桥LLC拓扑结构示意如下,需要2对PWM波。这里基于dsPIC33CH512MP508的从核实现,其中PWM1H和PWM1L为主管PWM驱动,PWM2H和PWM2L为同步管PWM驱动。

图 1 - 半桥LLC拓扑示意

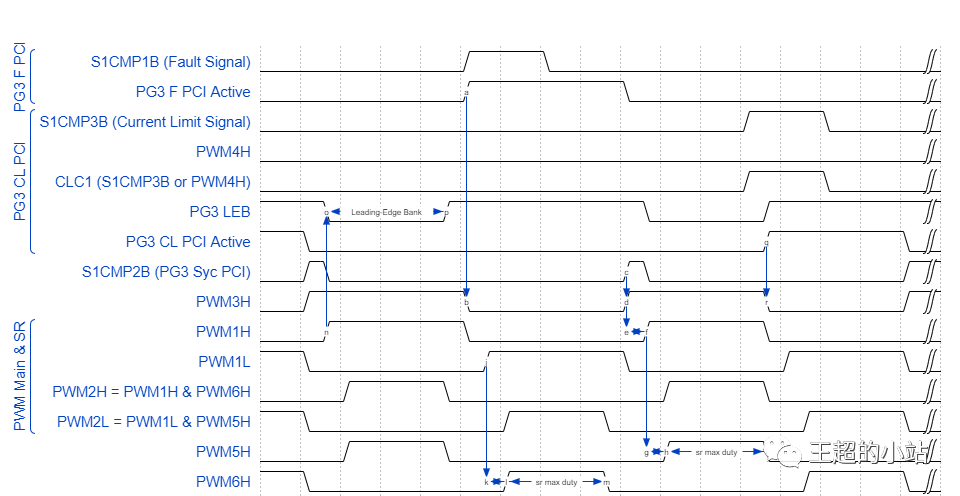

带同步整流的半桥LLC峰值电流控制的发波逻辑具体说明如下。

图 2 - 正常工作时PWM波形

主核的PWM1H(RB14)和PWM1L(RB15)在50kHz到350kHz来回滑动,为50%占空比互补模式无死区,以模拟外部输入信号。同时实验前需按如下规则接线,搭建好的平台如图6所示。注意:S1CMP3B与S1CMP1B连接的为同一个信号PWM1L,实验室也可以一个连接为PWM1L,一个连接为GND,以分别验证PG3的PCI限流和故障。

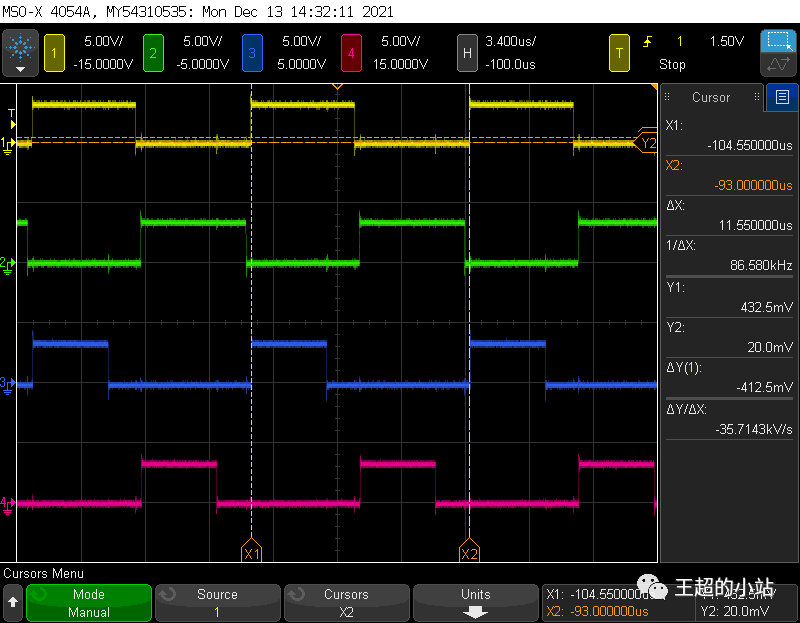

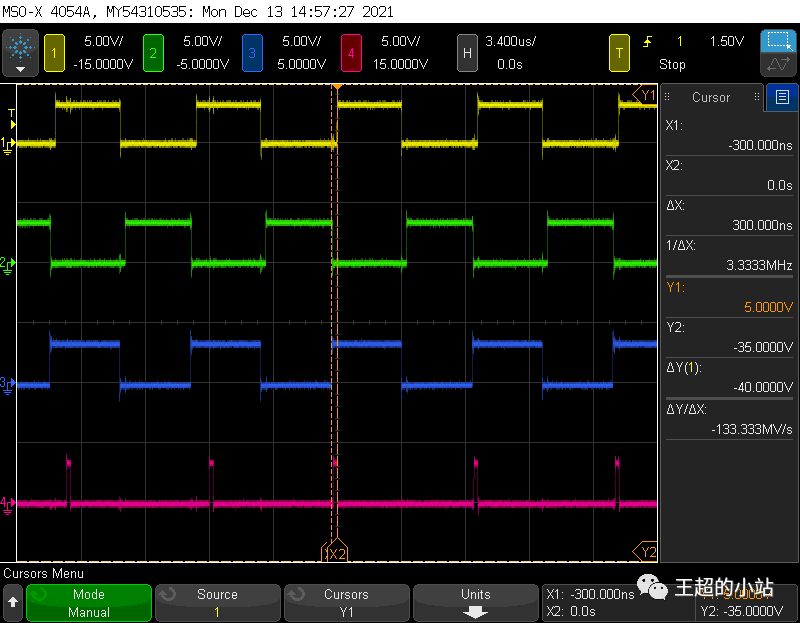

1)稳态时,同步管PWM2H和PWM2L被限制最大占空比工况波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

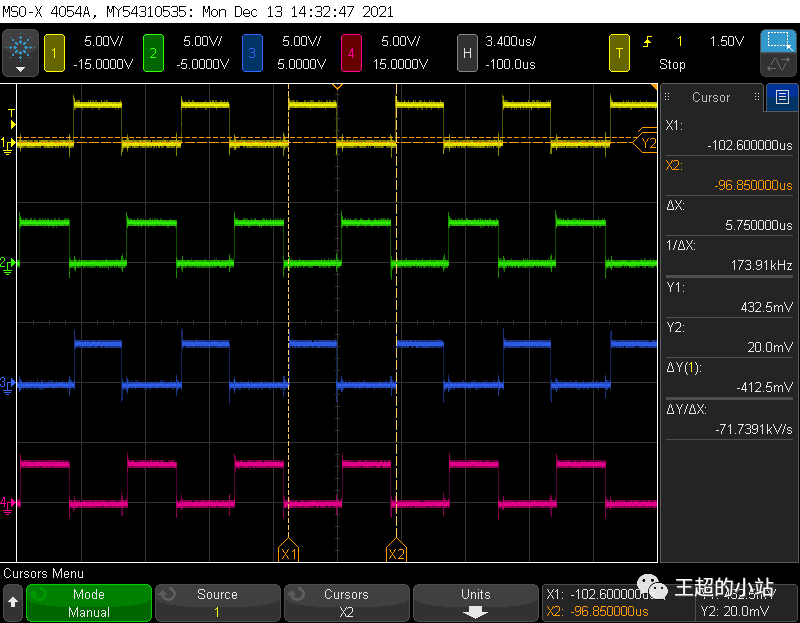

2)稳态时,同步管PWM2H和PWM2L未被限制最大占空比工况波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

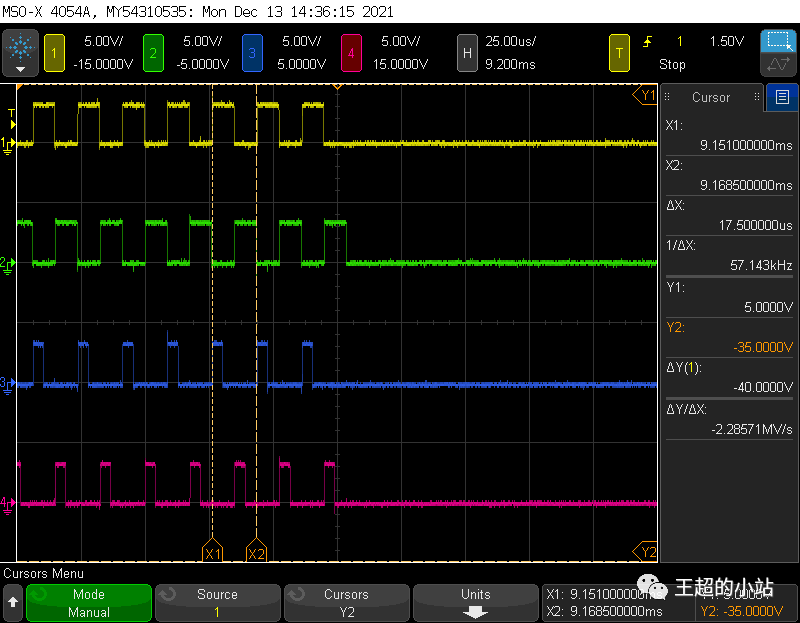

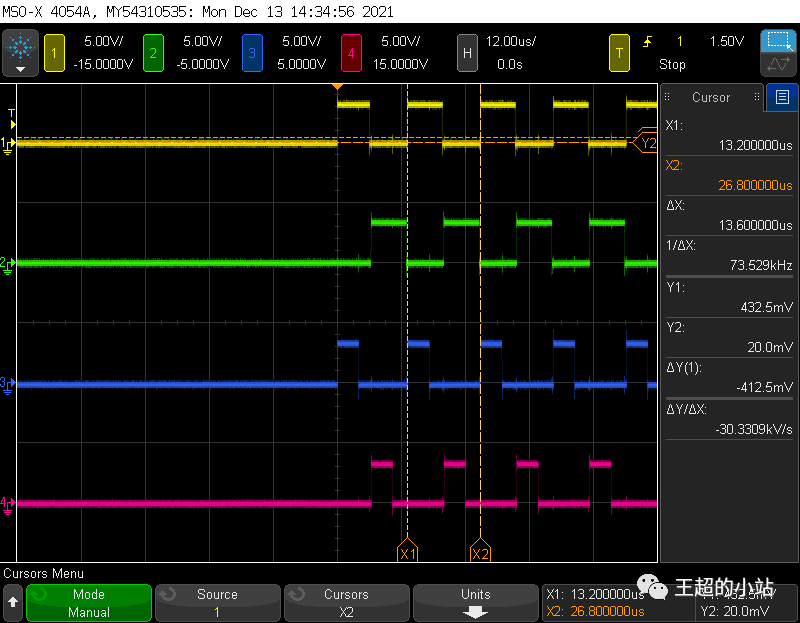

3)发波到禁止发波过程波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

4)发波禁止到发波过程波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

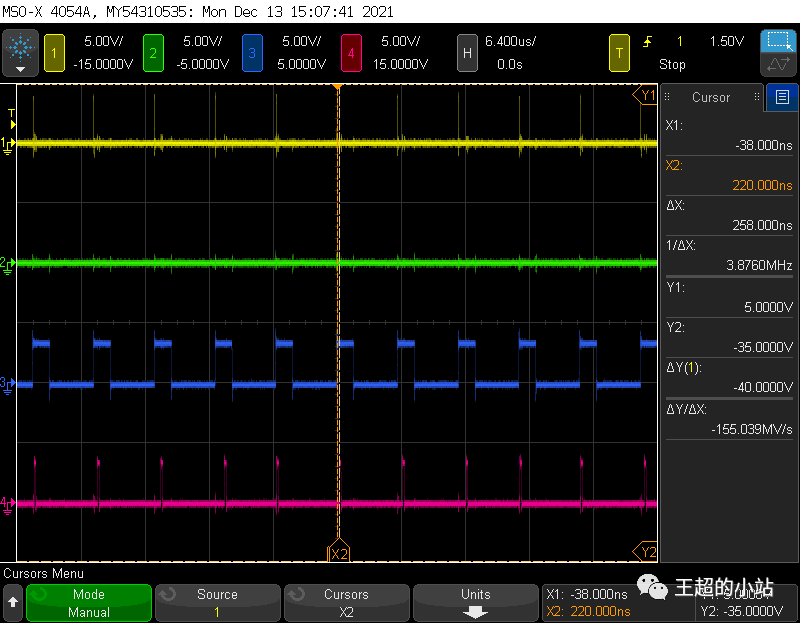

5)功率管发波期间PWM3H和PG3同步中断IO(RD0)翻转波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM3H, CH4: RD0

6)功率管非发波期间PWM3H和PG3同步中断IO(RD0)翻转波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM3H, CH4: RD0

注意:以上波形均未考虑同步管相对于主管的相位延迟,大家可以通过PG5PHASE和PG6PHASE自行设置。

下一篇:I2C和I3C的区别有哪些

从profibusDP转ModbusTCP,一网打尽转换技巧!