时间:2023-05-26 16:42

人气:

作者:admin

端口是模块与外界交互的接口,对外部环境而言,模块内部是不可见的,对模块的调用只能通过端口连接进行

端口基本语法约定如下:

端口必须被声明

端口声明不可重复

端口声明既可在端口列表内也可在列表外

模块间的数据只能通过端口进行

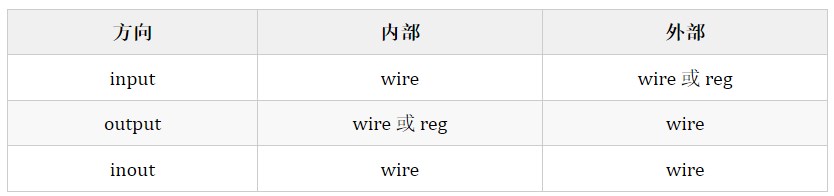

根据端口的方向,端口类型有3种:输入(input)、输出(output)和双向端口(inout)

wire型wire 也可以是 reg

regwirereg类型是用于保存数值的,而输入端只能反映与其相连的外部信号的变化,并不能保存这些信号的值

对于inpu和output我是这样理解的,内部是reg外部就应该是wire

就比如input这一端,外部是reg,内部是wire,在这个一端,已经有一个reg类型可以用来保存数据,不需要用到两个reg来保存数值

端口连接的方式有两种:按位置连接 和 按名称连接

//调用模块

module name(……);

//端口定义

//端口描述

/*a, b, c, d分别对用调用模块

中的in1, in2, sel, dout*/

mux u1(a, b, c, d);

endmodule

//调用模块

module mux (in1, in2, sel, dout);

//端口定义

//端口描述

//逻辑描述

endmodule

模块名 模块实例化名 (.被调用模块端口名(调用模块端口名));模块实例化名 是自己随意定的一个名字,方便记忆就好

//调用模块

module name(……);

//端口定义

//端口描述

//模块调用,也叫实例化

//对应方式和上一个相同

mux u1(.in1(a), .in2(b), .sel(c), .dout(d));

endmodule

//被调用模块

module mux(in1, in2, sel, dout);

//端口定义

//端口描述

//逻辑描述

endmodule

从profibusDP转ModbusTCP,一网打尽转换技巧!