时间:2023-05-26 18:08

人气:

作者:admin

在这里,我们描述了使用 Synopsys SoundWire VIP 测试套件集成和验证 SoundWire 设计是多么容易。

通常,验证IP和设计集成需要深入了解协议和方法。这需要投入大量时间来建立内部专业知识。为了加快这一过程,Synopsys 的 Soundwire VIP 解决方案采用 100% 原生 SystemVerilog 编写,以实现易用性、易于集成和高性能。此外,我们还提供完整、独立且经过设计验证的测试套件,采用 SystemVerilog UVM 编写,针对协议合规性测试。这些作为源代码提供,使用户能够轻松自定义或扩展环境,以包括独特的特定于应用程序的测试或极端情况方案。在某些情况下,使用 Synopsys VIP 和测试套件,我们的用户将验证时间从几个月缩短到几个小时。

声线测试套件架构

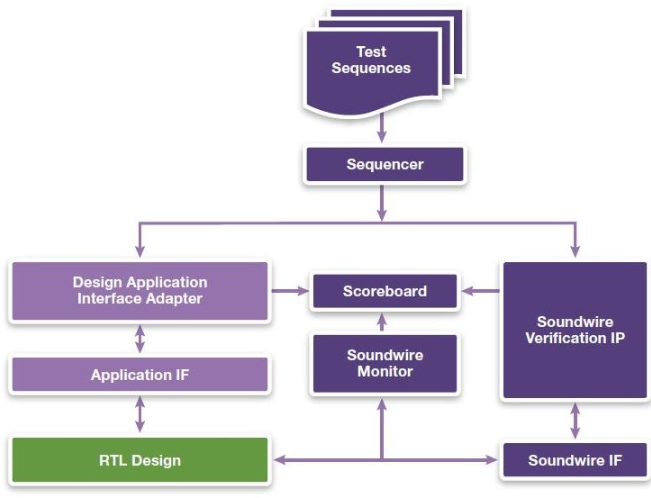

验证 IP 和 RTL 设计 集成 是 良好 的 测试 套件 架构 最 有帮助 的 领域 之一。如果测试套件环境的设计考虑到各种设计配置,则很容易插入带有验证IP的设计。下图说明了我们的测试套件体系结构。

此体系结构的目的是使环境设计独立,以便它可以毫不费力地与任何设计一起使用。在此图中,测试套件提供了深紫色和浅紫色色块,用户只需在浅紫色色框中进行干预即可根据特定的DUT自定义环境。这些更改是一次性更改,所有现有测试和序列都应在更改后按原样运行。这 显著 缩短 了 任何 设计 的 验证 时间, 同时 使 用户 能够 灵活 地 为 设计 特定 的 测试 场景 编写 自己的 测试 和 序列。

审核编辑:郭婷

上一篇:鳍式场效应晶体管FinFET

从profibusDP转ModbusTCP,一网打尽转换技巧!