时间:2020-11-13 15:17

人气:

作者:admin

作者:OpenSLee

1、Floating-Point IP支持的运算操作

1)Multiply—乘法

2) Add/subtract—加法和减法

3)Accumulator—累加

4) Fused multiply-add--融合乘加

5) Divide—除法

6)Square-root—平方根

7) Comparison—比较

8) Reciprocal—倒数

9)Reciprocal square root—倒数平方根

10)Absolute value—绝对值

11) Natural logarithm—自然对数

12)Exponential—指数

13)Conversion from floating-point to fixed-point—浮点转定点

14)Conversion from fixed-point to floating-point—定点转浮点

15) Conversion between floating-point types—浮点类型之间的转换

2、Floating-Point IP接口

如下图所示,Xilinx Floating-Point IP主要分为操作数s_axis_a,s_axis_b,s_axis_c,可编程操作s_axis_operation和输出结果m_axis_result。

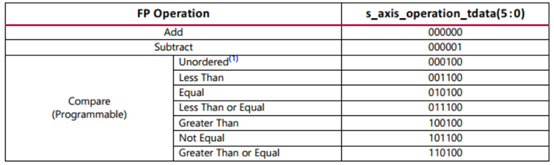

2.1 s_axis_operation_tdata

当我们同时选择加法和减法运算或选择可编程比较器时,将存在s_axis_operation通道。s_axis_operation_tdata的具体含义如下表所示。

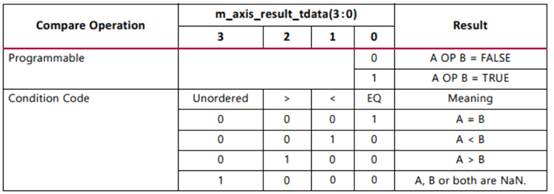

2.2 m_axis_result_tdata

如果是比较操作,则结果中的有效位取决于所选的比较操作。

3、AXI4-Stream Protocol

使用AXI4-Stream接口带来了标准化,并增强了Xilinx IP LogiCORE™解决方案的互操作性。除了诸如aclk,acclken和aseten之类的常规控制信号外,所有往返于浮点运算符核心的输入和输出均使用AXI4-Stream通道进行传输。通道始终由TVALID和TDATA以及几个可选的端口和字段组成。在浮点运算符中,支持的可选端口为TREADY,TLAST和TUSER。 TVALID和TREADY一起执行握手以传输消息,其中有效负载为TDATA,TUSER和TLAST。浮点运算符对TDATA字段中包含的操作数进行运算,并将结果输出到输出通道的TDATA字段中。浮点运算符本身并不使用TUSER和TLAST输入,但是内核提供了以与TDATA相同的延迟来传送这些字段的功能。预期该功能可简化系统中浮点运算符的使用。例如,浮点运算符可能正在处理流式打包数据。在此示例中,核心可以配置为通过分组数据通道的TLAST,从而节省了系统设计人员为该信息构建旁路路径的工作。

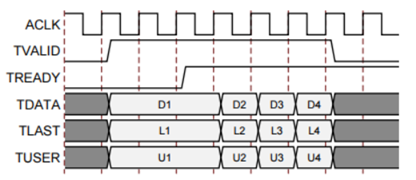

Basic Handshake:

如下图所示,在AXI4-Stream通道中的数据传输。 TVALID由通道的源(主)侧驱动,而TREADY由接收器(从属)驱动。 TVALID指示有效负载字段(TDATA,TUSER和TLAST)中的值有效。 TREADY表示从机已准备好接收数据。当TVALID和TREADY在一个周期中都为TRUE时,将发生传输。主机和从机分别为下一次传输分别设置TVALID和TREADY。

编辑:hfy

从profibusDP转ModbusTCP,一网打尽转换技巧!