时间:2018-01-12 11:48

人气:

作者:admin

许多FPGA设计都采用高速存储器接口,可能调试比较困难,不过只要采用正确的方法就能成功进行调试。

现代FPGA通常连接高速SRAM和SDRAM存储器。要确保这种器件无差错运行,调试起来可能比较困难。我们必须确保包括电路板布局、电源和FPGA中存储器接口电路等诸多因素准确无误,才能实现一款切实可行的存储器设计。

您在调试SRAM和SDRAM存储器时可能会遇到一些问题,而这些问题有可能会让您头疼好几天。设计和调试高速存储器接口时必须确保采用适当的调试方法。下面我将介绍的高效设计流程模型采用的是赛灵思Virtex®-4和Virtex-5 FPGA,然而Virtex-6和7系列器件也同样存在问题和相应的解决方案。我和同事采用赛灵思存储器接口生成器(MIG)工具来生成所有的存储器IP核,并通过赛灵思ISE®工具来进行设计的综合和布局布线。在详细分析特定设计的特性之前,我们不妨先来看看赛灵思MIG工具、针对赛灵思FPGA的存储器校准过程以及我们用来验证存储器接口设计的内建自测试(BIST)电路。

赛灵思提供存储器接口生成器工具为其FPGA器件生成存储器接口内核。

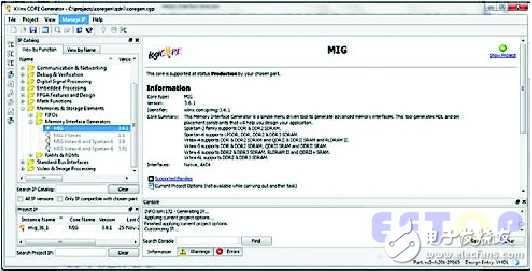

从赛灵思CORE Generator™调用的MIG工具可为DDR-II SRAM、DDR2 SDRAM和QDR-II SRAM等各种类型存储器生成接口。图1显示了赛灵思CORE Generator屏幕截图,详细介绍了MIG3.6.1中支持的赛灵思器件系列和存储器。此外,还有一款7系列MIG工具可支持赛灵思最新器件。

MIG通过图形用户界面(GUI)输入存储器和FPGA类型的详细信息,最后生成VHDL语言或Verilog语言的寄存器传输级(RTL)文件,以及有关存储器接口的用户约束文件(UCF)。您可将这两类文件与设计方案的其它部分进行综合。此外,MIG还可生成基础架构模块,为存储器接口提供所需的时钟和复位。此外,该工具还提供测试平台电路,可用来生成存储器器件的读写操作,以验证正常运行。您可从赛灵思网站下载MIG工具及其支持的FPGA和存储器的完整介绍。

为了确保从存储器准确捕获数据到FPGA中,存储器接口内核应在使用读取数据路径前对其进行校准。校准过程在加电时自动进行。基本而言,数据训练模式被写入到存储器中,随后不断读回。这是过程分三个阶段:第一阶段要让读取数据窗口相对于数据选通信号居中,对进入FPGA的数据进行计时;第二阶段要确保居中的数据和时钟同步于FPGA时钟域,从而使数据能在输入触发器和FPGA架构中的触发器之间传输;第三阶段则提供读取验证信号。赛灵思MIG文档全面介绍了各种不同类型的存储器校准过程。

图1- CORE Generator MIG工具支持多代赛灵思FPGA。

我们采用赛灵思MIG工具生成所有存储器接口设计。不过在一些设计实例中我们则不用MIG工作流程。我们使用的FPGA所在的电路板是针对各种用户和应用设计的。因此我们要设计一个定制时钟生成器与复位模块,提供用户应用所需的所有时钟和复位。这意味着应移除MIG生成的基础架构模块并从我们的定制模块为存储器接口提供时钟和复位。

从profibusDP转ModbusTCP,一网打尽转换技巧!