时间:2011-08-31 15:02

人气:

作者:admin

引言

本文提出了一种基于PCI Express总线接口的、具备可扩展性能、并可大容量存储数据的采集系统。该系统的最高采样速率可达80 MHz,利用计算机并通过PCI Express总线和采集卡、Raid磁盘阵列相连后,便可通过主机软件界面实现对硬件设备的控制。

1 系统结构

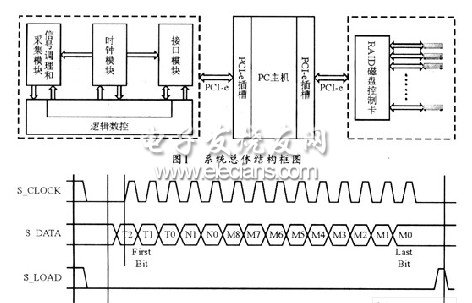

方案总体上分为三个部分:高速信号采集卡、主机、Raid磁盘阵列,他们之间可通过PCIExpress总线连接。其系统结构如图1所示。

本系统的高速信号采集卡主要由信号调制电路、数据采集模块、采集时钟控制模块、数据缓存和逻辑控制模块、PCI Express总线接口控制等部分组成。其中逻辑控制模块负责接收来自PCIExpress接口的主机控制信息以及采样时钟频率的控制信号,并向系统的其它部分发送相关的控制命令。在进行数据采集时,A/D转换芯片的输出在经过信号处理后,可在数据缓存模块的控制下存入FPGA内部FIFO中;然后再通过PCI Express总线通过主机内存转存到Raid磁盘阵列。

2 系统实现

2.1 数据采集

本系统中的数据转换芯片采用ADI公司生产的AD9430流水型转换器。它是一种单片低功耗12位高速ADC器件,采用3.3 V单一电源供电,具有最大的高速转换率(能够达到210 MSPS),并在较宽的频带范围内仍然具有较好的动态特性。另外,片内还集成了高性能的采样保持放大器、参考电压源和数据时钟输出信号。可为系统提供更加简捷的解决方案。

AD9430有两种数据输出接口模式,即3.3VCOMS输出和LVDS输出。AD9430正常工作后,每个时钟周期进行一次A/D转换,当通过内部缓冲采样保持器和编码之后,可将转换结果锁存到输出寄存器。

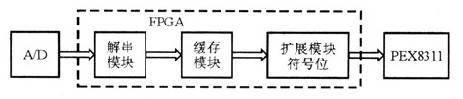

通常高速数据采集都是建立在高速高精度采样的基础之上,而高速采样必须得到高质量时钟信号的保障。采样时钟发生电路是高速AD采样的基础模块。本系统选用可程控时钟源SY89429AZC来产生AD9430的采样时钟,并通过对SY89429AZC芯片S_CLOCK、S_DATA、S_LOAD三个引脚信号线的控制,来程控输出40MHz~200MHz精确采样时钟。图2所示是SY89429AZC的三线控制时序图。

TTL引脚S_DATA为配置串行移位寄存器的输入端,串行寄存器可在每一个S_CLOCK信号的上升沿对S_DATA信号进行取值。另有一配置锁存器可在S_LOAD信号为高电平时锁存串行移位寄存器的内容。这样,通过设置S_DATA信号的值(即T2…T0,N1,N0,M8…M0的数值)以及三信号线的时序,便可控制SY89429AZC时钟芯片输出精确的采样时钟。

上一篇:总线实现片内硬件调试支持单元设计

从profibusDP转ModbusTCP,一网打尽转换技巧!