时间:2023-08-01 09:37

人气:

作者:admin

大家都知道锁相环很重要,它是基石,锁相环决定了收发系统的基础指标,那么如此重要的锁相环选型原则有哪些呢?

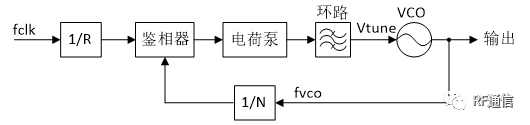

锁相环原理

锁相环一般由鉴相器(PD)、环路滤波器(LPF)、电压控制振荡器(VCO)组成。其功能如下:

鉴相器:又称为相位比较器,其主要功能是检测输入信号和输出信号的相位差,并将检测的相位差转换为电压信号。

环路滤波器:主要功能是滤除鉴相器输出的高频分量。

电压控制振荡器:根据鉴相器产生的信号,对输出信号的频率和相位进行调整。

基本原理大家都知道

相位噪声

相位噪声是第一设计原则

相位噪声的计算公式

F=FOM + 10logfpfd+ 20log N

FOM是归一化相位噪声。

从上述公式可以看出,除了FOM,相位FPD和N有关,输出频率定下来之后我们可以发现,相位噪声与FPD关系最大。

因此在不考虑基带采样率因素的情况下,FPD越大越好。

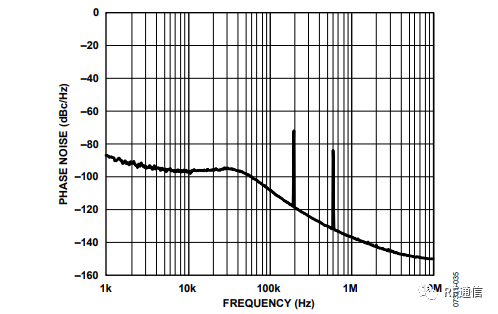

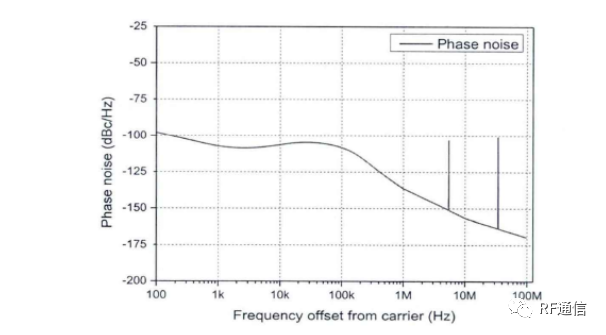

上图是闭环相位噪声

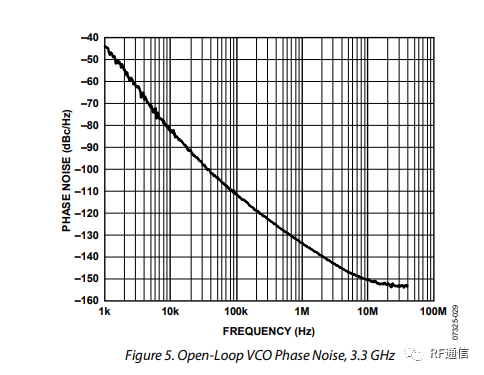

注意此公式用来计算带内相位噪声,带外与VCO的相噪有关。在设计与邻道相关的指标时考虑的就是带外相位噪声,说白了就是VCO的相位噪声。一般器件的手册会给一个典型频点的相噪,可以根据手册的指标按照20lg(f/f2)估算所需频段的相位噪声。

例如下图,3.3G在200k位置是-120dBm/Hz,那么1G在200k的位置就是-129dBm/Hz左右。

所以选型第一原则就是在可选范围内,选择PD的频率越高越好。

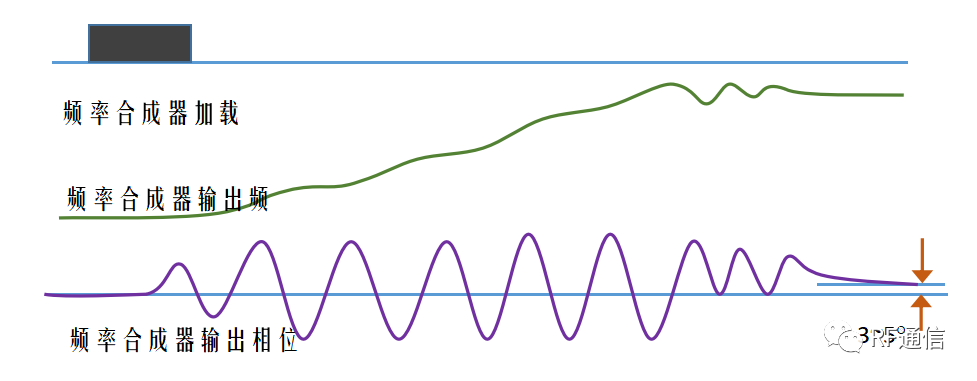

锁定时间

锁定时间老生常谈,注意一下,锁定时间除了物理换频时间还要加上程序加载时间。

杂散的规避方法

散是锁相环避不开的问题。杂散分为小数杂散和整数杂散,杂散存在不可怕,只要有应对的办法就好。

小数杂散

小数锁相环是目前锁相环的主流应用,小数杂散的来源主要有以下几种

鉴相杂散

泵电流杂散

小数杂散的降低主要从以下入手:1.改变小数分频比2.改变鉴相频率

总的原则就是改变小数杂散的相对位置,然后通过低通滤波器压制。

注意:小数杂散出现频率很高,需要大量的测试验证通过去规避。

整数杂散

当设计宽频方案时,整数杂散不得不考虑,因为整数杂散无法消除,一定会存在。

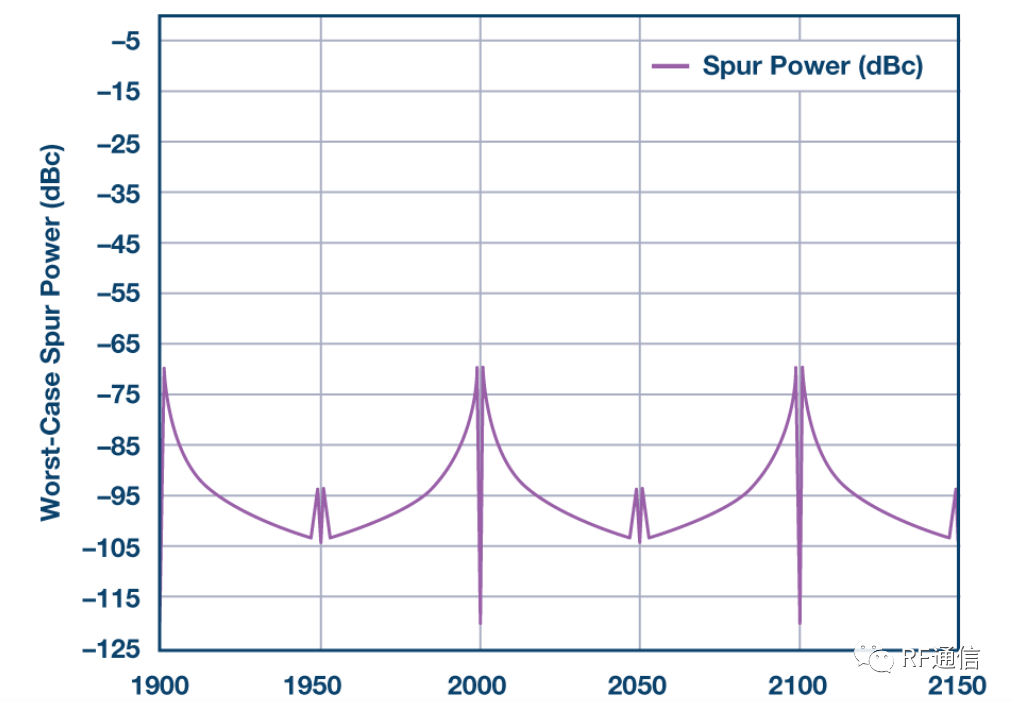

整数边界杂散发生在PFD频率的整数倍处,并且在接近载波频率时最强。

此时环路滤波器无法将其滤除。

例如,参考输入为 20 MHz,假设输出频率为1000.1MHz,那么就会产生1000MHz的整数杂散,也可以看到,整数杂散间隔20MHz就会出现。

整数杂散很规律,非常容易发现。

解决的办法有两种

增加环路滤波器阶数

但是效果一般,环路滤波器带外抑制效果一般,增加阶数可能会带来环路不稳定的因素。

改变鉴相频率

以上文为例,鉴相频率为20MHz,在输出1000.1MHz时会出现整数杂散,那么改变鉴相频率为30MHz,1001.1MHz就不会出现。

所以需要选择鉴相频率可奇偶数可除的锁相环。

设计宽频方案时,此点非常重要,并不是所有锁相环都可鉴相奇偶数可除。

总结

当下的锁相环无需复杂的设计,十年前还需要设计外置VCO,现在频率源很多都不单独设置专门的岗位。仅需要做好选型工作就好,在此情况下我们不能再退。

审核编辑:刘清

NVIDIA RTX PRO 4500 Blackwell GPU测试分析