时间:2023-10-31 09:50

人气:

作者:admin

该实验可以作为DDS Compiler IP核的使用典例

背景知识

混频原理

混频就是把两个不同的频率信号混合,得到第三个频率。在模拟电路中经常见到的就是把接收机接收到的高频信号,经过混频变成中频信号,再进行中频放大,以提高接收机的灵敏度。

数字电路中最简单的混频便是两个信号做乘法,可以得到它们的和频信号与差频信号。数字混频在通信的调制、解调、DUC(数字上变频)、DDC(数字下变频)等系统中应用广泛。通常把其中一个信号称为本振信号(localoscillator),另一个信号称为混频器的输入信号。

NCO&DDS

NCO是Altera公司Quartus中的NCOIP核[Numerically controlledoscillators数控振荡器]

DDS是Xilinx公司Vivado中的DDSCompiler IP核[Direct DigitalSynthesizers直接数字合成器]

NIOS&ARM

NIOS是Altera公司推出的,是为了配合FPGA而设计的

ARM是Xilinx公司集成的,集成的目的也是为了方便FPGA的使用

它们都是嵌入式处理器

程序设计

设计思路

程序设计系统时钟5MHz,625kHz的输入信号与625kHz的本振信号做混频,根据混频原理会得到1.25MHz的和频信号与0Hz(直流),将直流滤除掉得到1.25MHz的有效信号。

如何滤除直流信号?

隔离直流信号最常用的方法就是用电容进行隔直!

就是在前后级电路之间串接一个电容,电容的充放电时间要大于信号频率。

以下滤除直流信号部分将采取一种比较特殊的方式!

顶层模块接口

module Mixer

(

input clk, //5MHz系统时钟

input rst_n, //低电平有效复位信号

input [9:0] din, //输入信号

output [9:0] s_oc, //本振信号,625kHz

output out_valid, //NCO输出有效信号

output [19:0] dout //混频输出信号

);

生成本振信号

wire [9:0]oc_sin;

oc oc

(

.phi_inc_i (16'd8192), //相位增量,对应625kHz

.clk (clk),

.reset_n (rst_n),

.clken (1'b1), //时钟允许信号

.fsin_o (oc_sin), //本振正弦信号

.out_valid (out_valid) //输出有效标志

);

混频

接下来用乘法进行混频。我们都知道计算机中有带符号数signed和无符号数unsigned,还知道计算机经常以二进制补码的形式表示带符号数。

在FPGA设计中,不管是Altera还是Xilinx,它们的IP核几乎都是采用二进制补码带符号数,也有很多的ADC、DAC芯片的数据接口也采用的是二进制补码。因此,在设计中,我们要清楚什么时候用什么数值表示法。

滤除混频后的直流信号

由于5Mhz的系统时钟是625kHz信号的8倍,所以连续8个点的平均值便是直流分量

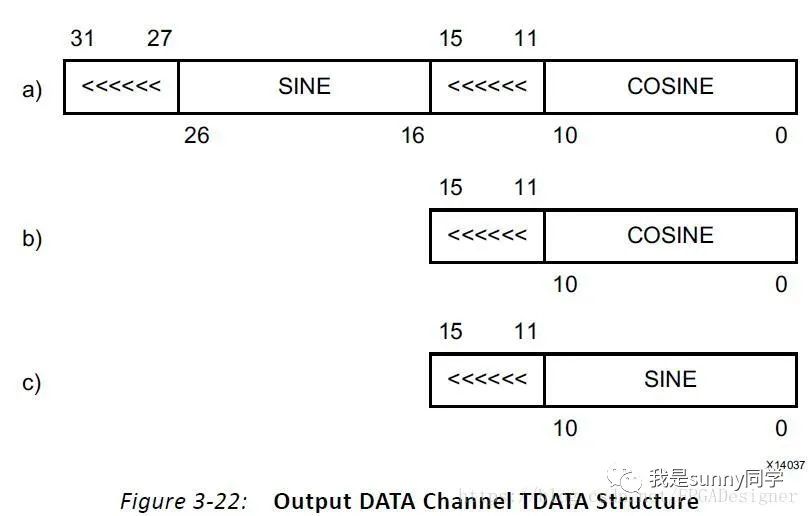

DDS Compiler IP核的使用

基本配置

位宽问题

产生sin与cos信号

产生带有相位偏移的信号

下一篇:如何避免晶体管损坏?

龙腾半导体SGT MOSFET LSGT085R018在智慧农业无