时间:2023-08-23 15:19

人气:

作者:admin

实训题目:计时器的设计

1 系统设计

1.1设计要求

1.1.1 设计任务

设计并制作一台计时器。

1.1.2 性能指标要求

① 用EDA实训仪的I/O设备和PLD芯片实现计时器的设计。

② 计时器能够显示时、分和秒。

③ 用EDA实训仪上的8只八段数码管显示时、分和秒(如00123625)。

④ 计时器具有复位和校准时、分、秒的按钮。

1.2 设计思路及设计框图

1.2.1设计思路

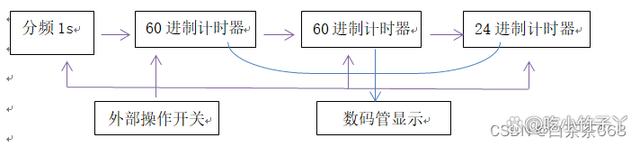

使用两个六十进制计数器和一个二十四进制计数器,设计出了一个24小时计时器系统。

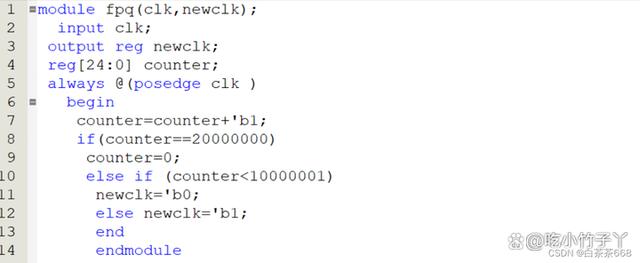

输入CLK为1Hz(1s)的时钟,经过60分频后产生1分钟时钟信号,再经过60分频后产生1小时的时钟信号,最后进行24分屏得到1天的脉冲送cout输出。

将两个60分频和一个24分频的输出送8段数码管,得到24小时的计时显示。

1.2.2总体设计框图

CLK是1Hz时钟输入端。clrn复位输入端,低电平有效。jm,jf,js分别是秒,分,时的时输入端,下降沿有效。分别是秒分时的计时输出端。cout是脉冲输出端。

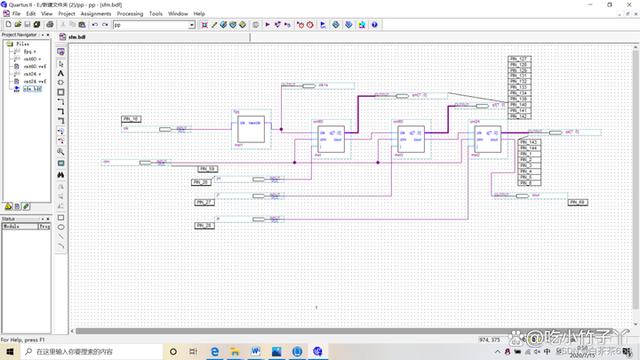

各个模块程序的设计

调试过程

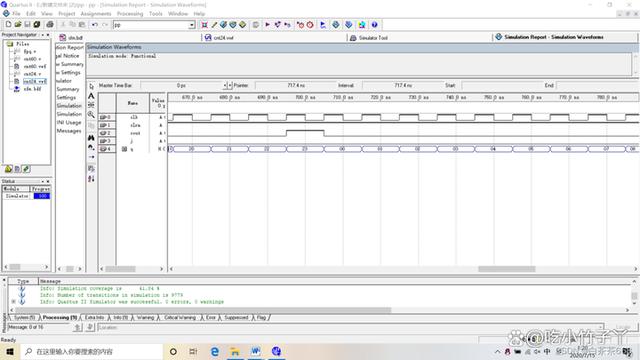

在电脑上设计好的工程,进行编译,编译成功后进行仿真,仿真成功后生成元件并加入到bdf中,找出相应的输入输出并与模块连接好,置顶并编译,提前锁好相应的管脚。在实验室使用Quartus 软件调试,在软件中open project打开设计好的工程,还需要对bdf进行一次置顶编译下载到实验箱。

找到锁好的管脚的拨码开关或按键。拨动相应的拨码开关实现计时器的复位功能,按动jm,jf,js所锁的按键可实现时、分、秒校准。实训过程中也会出现一些错误,如无法实现23计数归0,后发现是因为程序问题,修改后调试成功。

4 功能测试

4.1 测试仪器与设备 计算机。 EDA实验箱。

4.2 性能指标测试

能按实验要求实现8只八段数码管显示(例如00235959)并具有复位和校准时、分、秒和23时亮灯警告。

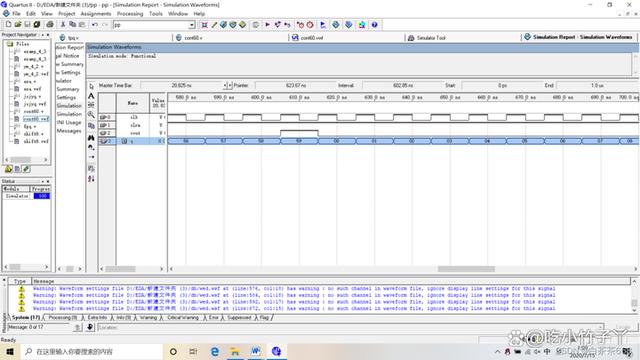

附录1:仿真波形图(部分模块)

龙腾半导体SGT MOSFET LSGT085R018在智慧农业无