时间:2023-03-28 10:13

人气:

作者:admin

1 三极管和MOS管的基本特性

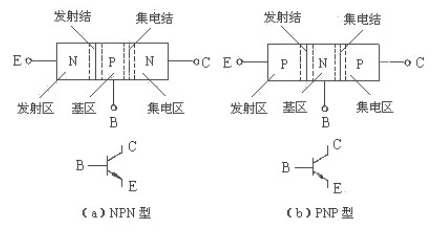

三极管是电流控制电流器件,用基极电流的变化控制集电极电流的变化。 有NPN型三极管和PNP型三极管两种,符号如下:

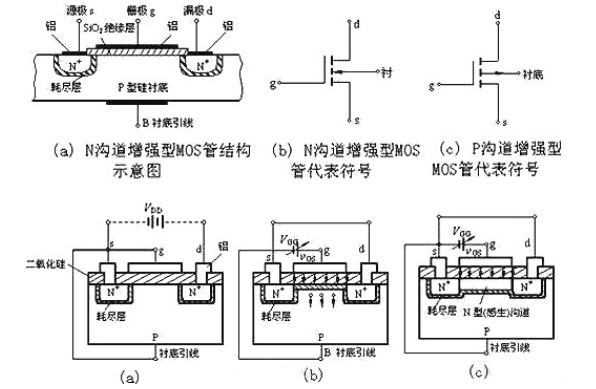

MOS管是电压控制电流器件,用栅极电压的变化控制漏极电流的变化。 有P沟道MOS管(简称PMOS)和N沟道MOS管(简称NMOS),符号如下(此处只讨论常用的增强型MOS管):

2 三极管和MOS管的正确应用

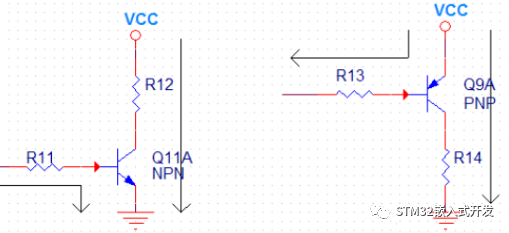

(1)NPN型三极管

适合射极接GND集电极接负载到VCC的情况。 只要基极电压高于射极电压(此处为GND)0.7V,即发射结正偏(VBE为正),NPN型三极管即可开始导通。 基极用高电平驱动NPN型三极管导通(低电平时不导通); 基极除限流电阻外,更优的设计是,接下拉电阻10-20k到GND;

优点是:①使基极控制电平由高变低时,基极能够更快被拉低,NPN型三极管能够更快更可靠地截止; ②系统刚上电时,基极是确定的低电平。

(2)PNP型三极管

适合射极接VCC集电极接负载到GND的情况。 只要基极电压低于射极电压(此处为VCC)0.7V,即发射结反偏(VBE为负),PNP型三极管即可开始导通。 基极用低电平驱动PNP型三极管导通(高电平时不导通); 基极除限流电阻外,更优的设计是,接上拉电阻10-20k到VCC;

优点是:①使基极控制电平由低变高时,基极能够更快被拉高,PNP型三极管能够更快更可靠地截止; ②系统刚上电时,基极是确定的高电平。

所以,如上所述:

对NPN三极管来说,最优的设计是,负载R12接在集电极和VCC之间。 不够周到的设计是,负载R12接在射极和GND之间。

对PNP三极管来说,最优的设计是,负载R14接在集电极和GND之间。 不够周到的设计是,负载R14接在发射极和VCC之间。 这样,就可以避免负载的变化被耦合到控制端。 从电流的方向可以明显看出。

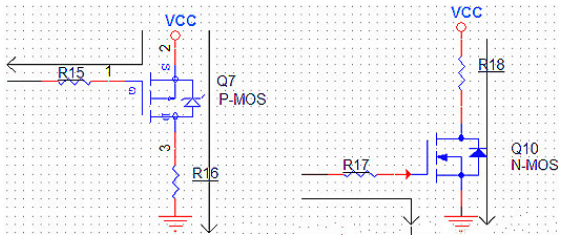

(3)PMOS

适合源极接VCC漏极接负载到GND的情况。 只要栅极电压低于源极电压(此处为VCC)超过Vth(即Vgs超过-Vth),PMOS即可开始导通。 栅极用低电平驱动PMOS导通(高电平时不导通); 栅极除限流电阻外,更优的设计是,接上拉电阻10-20k到VCC,使栅极控制电平由低变高时,栅极能够更快被拉高,PMOS能够更快更可靠地截止。

(4)核磁阻

适合源极接GND漏极接负载到VCC的情况。 只要栅极电压高于源极电压(此处为GND)超过Vth(即Vgs超过Vth),NMOS即可开始导通。 栅极用高电平驱动NMOS导通(低电平时不导通); 栅极除限流电阻外,更优的设计是,接下拉电阻10-20k到GND,使栅极控制电平由高变低时,栅极能够更快被拉低,NMOS能够更快更可靠地截止。

所以,如上所述:

对PMOS来说,最优的设计是,负载R16接在漏极和GND之间。 不够周到的设计是,负载R16接在源极和VCC之间。

对NMOS来说,最优的设计是,负载R18接在漏极和VCC之间。 不够周到的设计是,负载R18接在源极和GND之间。

3 设计原则

为避免负载的变化被耦合到控制端(基极Ib或栅极Vgs)的精密逻辑器件(如MCU)中,负载应接在集电极或漏极。

审核编辑:汤梓红

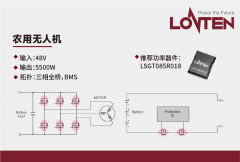

龙腾半导体SGT MOSFET LSGT085R018在智慧农业无