时间:2023-02-08 16:09

人气:

作者:admin

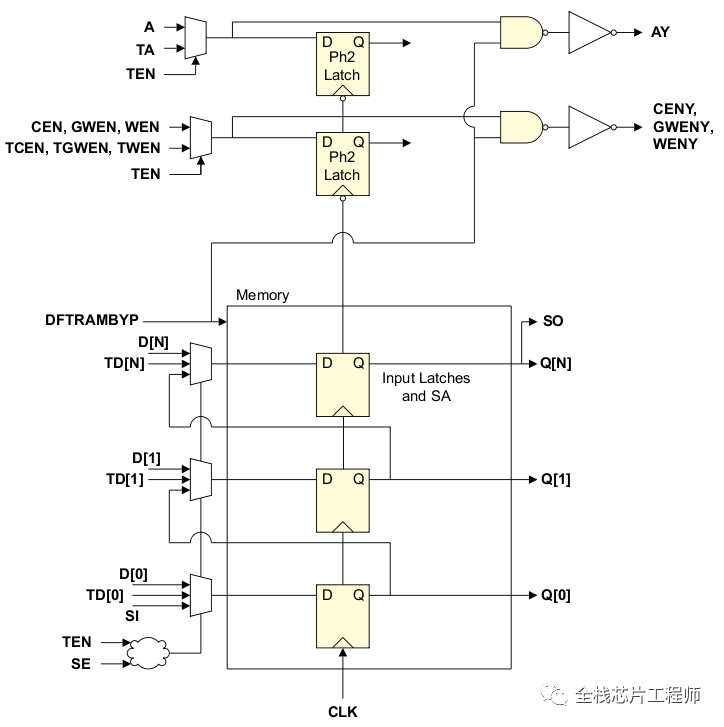

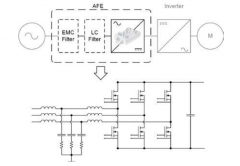

SRAM的MBIST测试结构如下:

SRAM的MBIST测试波形:

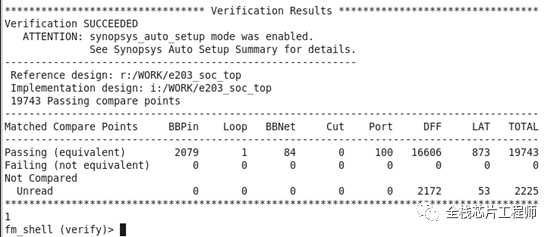

SRAM BIST电路完成插入后,需要做一个formal check,保证Mbist插入后,logic function不发生错误改变。Formal check需要注意常量设置,具体参见知识星球的详细解释。

此处分享2个经典问题:

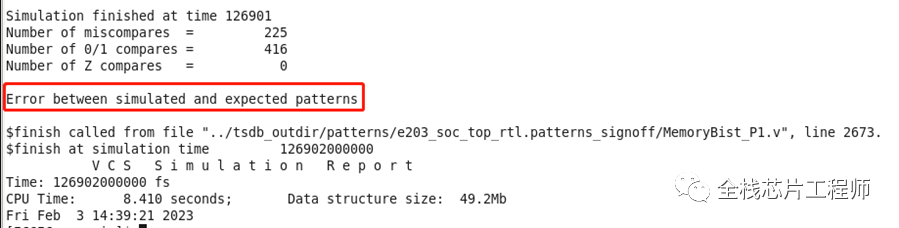

定位1:

通过trace TDO信号,一直追踪到SRAM的Q端,发现Q端数据输出是X态,通过分析发现本质上还是时钟问题,什么问题呢?

就是SRAM MBIST_CLK延时下来刚好和SRAM测试地址TADDR的跳变完全对齐了,造成了SRAM的memory model的建立/保持时间违例,SRAM model在timing违例情况下Q端输出为X态。下文具体内容请移步知识星球查看。

欢迎加入【全栈芯片工程师】知识星球,手把手教你设计MCU、图像传感器、ISP图像处理,从算法、前端、DFT到后端全流程设计。

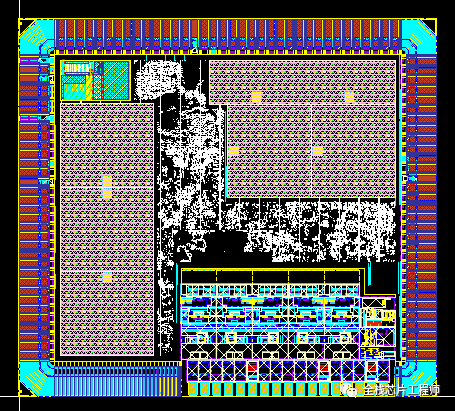

实战MCU+ISP图像处理芯片版图

实战ISP图像算法效果

审核编辑 :李倩

下一篇:A类放大器优缺点

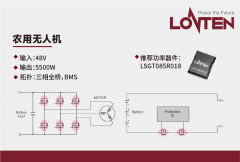

龙腾半导体SGT MOSFET LSGT085R018在智慧农业无