时间:2021-05-10 08:05

人气:

作者:admin

当读者和DI贡献者Jim Brannan建议编写他的base-3 DAC设计时,我感到非常高兴。像Charlieplexing一样,他的想法是利用三态输出来从引脚中拧出更多的信息,而不仅仅是“ 0”和“ 1”!例如,一个四位的DAC理论上可以产生34(81)个电平,而不是通常的16个电平。五个位实际上将与常规的八位性能(243个电平)相匹配,尽管精确的实现可能会更多。比常规的二进制DAC困难,尤其是随着分辨率的提高。

像往常一样,我到处搜寻Google的现有技术,是的,发现有两个页面描述了类似的野兽。吉姆看了一眼,并决定他没有什么要补充的,所以……没有“设计理念”。但是我觉得这个概念还是值得宣传的。吉姆也有自己独特的方法。

在继续之前,也许花点时间想象一下如何实现三元DAC。也许您会想出一个新的变体,然后再将下面的想法弄清楚。

好的,这是我自己的实现想法:

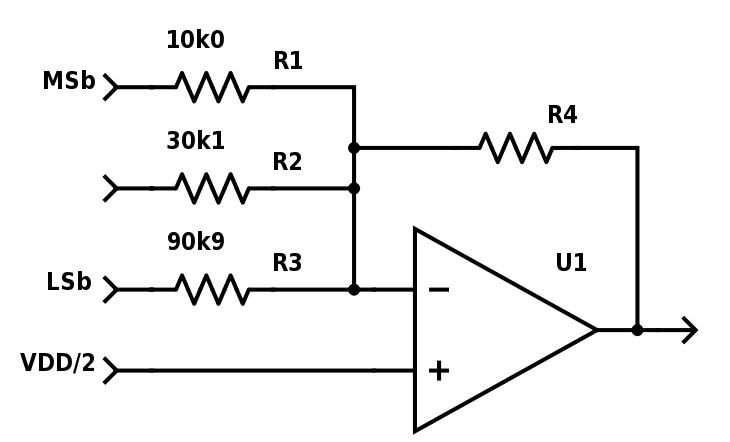

图1 具有中间电源基准的求和放大器实现了一个3基数DAC。

实际上,我最初的想法是在-VDD处输入放大器的(+)输入,但随后我意识到一个浮动输出将被拉向该负电源,可能钳位在-0.7V,并且通常不起作用。VDD/ 2参考表示0,1,2状态对应于0,Z,1输出(“ Z”表示高阻抗和/或输入模式)。

另一个硬件问题是,当输入处于中轨时,某些微控制器可能会消耗过多的电源电流,因此请确认这不是问题,禁用数字输入模式,或者使用可以设置为模拟输入的引脚。

驱动三进制DAC将需要查找表或二进制到三进制的转换例程。在大多数情况下,除非可以在一个写周期内设置引脚模式和值,否则更改其设置后,DAC输出就会出现毛刺。

吉姆(Jim)中止的“设计理念(Design Idea)”使用无源“ R-2R”型DAC,他编写了软件来搜索许多电阻器组合。无法创建完美的线性DAC,他的解决方案是使用查找表,并且性能有些不均匀。

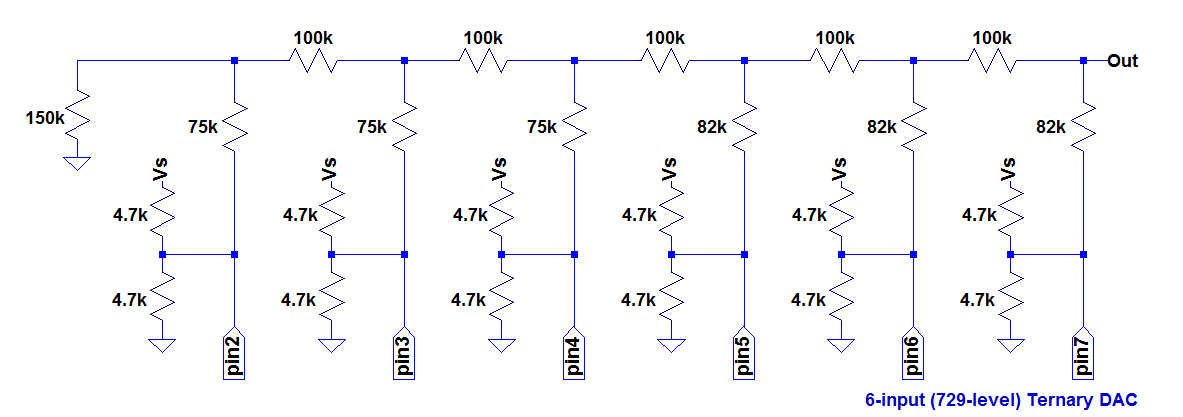

乔什·鲍曼(Josh Bowman)在他的博客中描述了自己对3进制DAC的看法。结构为R-2R-ish,其中较小值的电阻器将电源分开,以生成中间电平的“ Z”值。

图2 乔什·鲍曼(Josh Bowman)的无源三元DAC

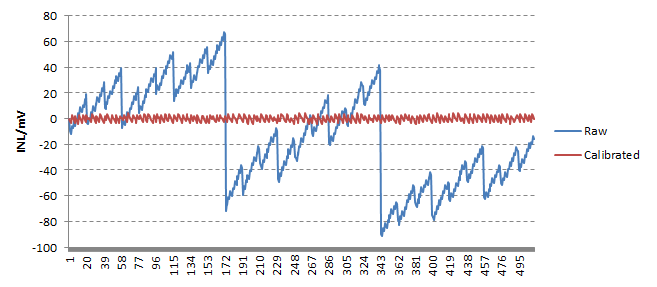

如下所示,设计中存在冗余值,可以进行校准。

图3原始和校准的INL性能

在此Arduino论坛上还讨论了一些基于base-3的DAC设计,这些是上述设计的变体。

如果尝试三元DAC实现,请在下面重新叙述您的经验。我们希望知道这一点。记住,与所有这些简单的DAC设计一样,电源噪声会传递到输出。

编辑:hfy

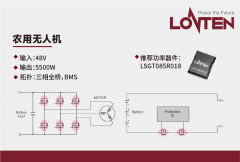

龙腾半导体SGT MOSFET LSGT085R018在智慧农业无