时间:2023-09-13 17:32

人气:

作者:admin

目前很多芯片都会有几个core核,有的是CortexM0+、M4、M7、A53、A73等等,有的有着2核、3核、4核甚至6核8核,不同的核的主频支持度不一样,适用的具体应用场景也不同,因此需要IPC(Inter-processor communication)来核间通信,进行数据的交互。

核间通信(IPC)的主要目标是:充分利用硬件提供的机制,实现高效的CORE间通信;给需要CORE间通信的应用程序提供简洁高效的编程接口。

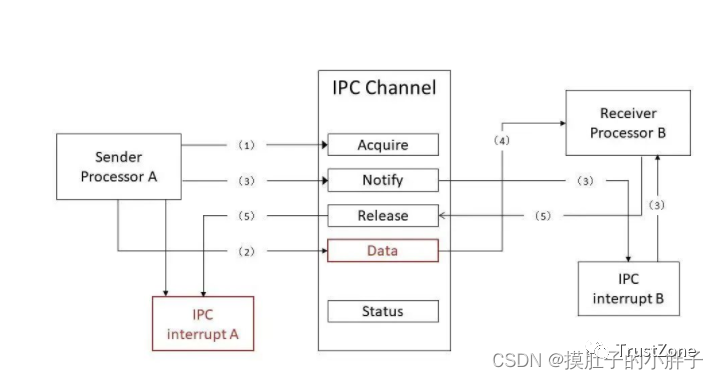

根据所使用的硬件特性,核间通信的实现机制有:

• ·Mailbox中断

• ·基于共享内存的消息队列

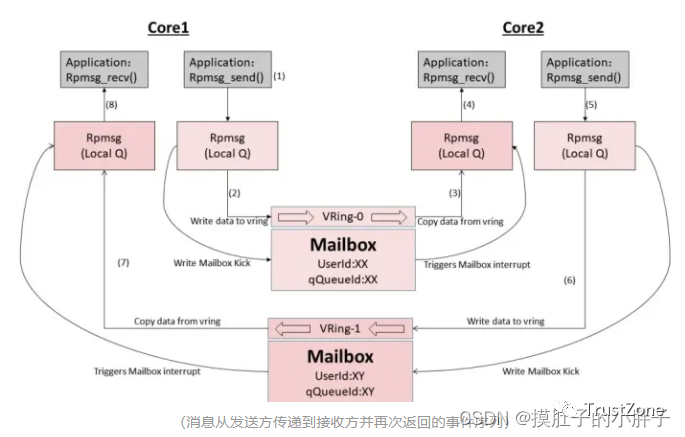

封装-VRING-解析的过程:1、应用程序向给定目的地(CPU、端点)发送消息

2、消息首先从应用程序复制到两个CPU之间使用的VRING。此后,IPC驱动程序在硬件邮箱中发布 VRING ID。

3、这会触发目标 CPU 上的中断。在目标 CPU 的 ISR 中,它提取 VRING ID,然后根据 VRINGID 检查该 VRING

中的所有消息。

4、如果收到消息,它从VRING中提取消息并将其放入目标RPMSG端点队列中。然后触发在此 RPMSG端点上阻止的应用程序。

5、应用程序处理接收到的消息,并使用相同的RPMSG 和VRING 机制在相反方向回复发送方CPU。

下一篇:SoC的核间通信机制硬件邮箱