时间:2023-07-05 10:49

人气:

作者:admin

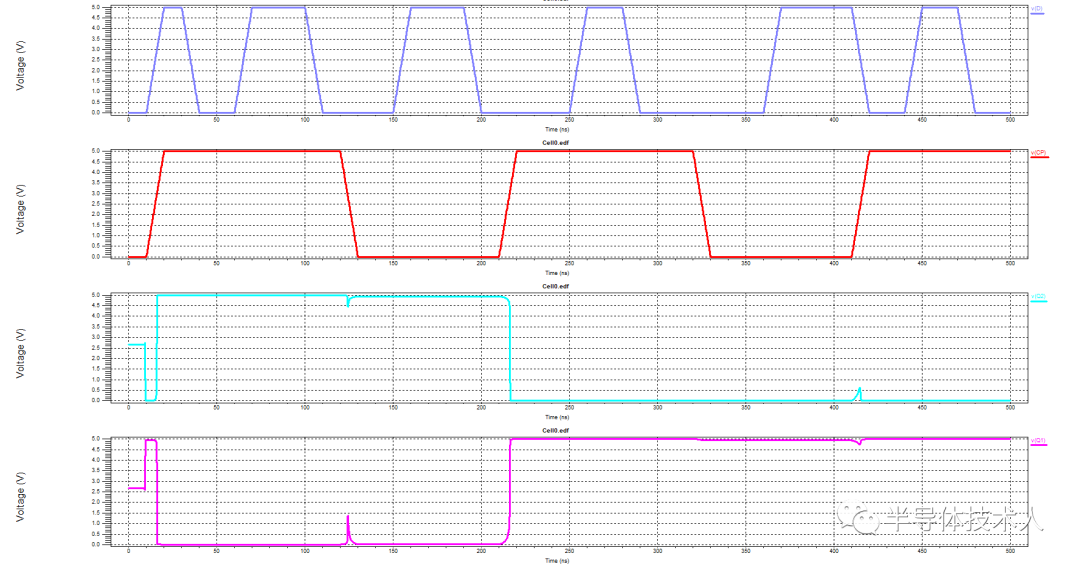

数字系统往往是由多个触发器所组成,这时常常需要各个触发器按照一定的节拍同步动作,因此必须给电路加上一个统一的控制信号。这个统一的控制信号叫做时钟脉冲,简称CP。同步触发器又称钟控触发器,即时钟控制的电平触发器。

D 触发器:D锁存器和维持-阻塞D触发器

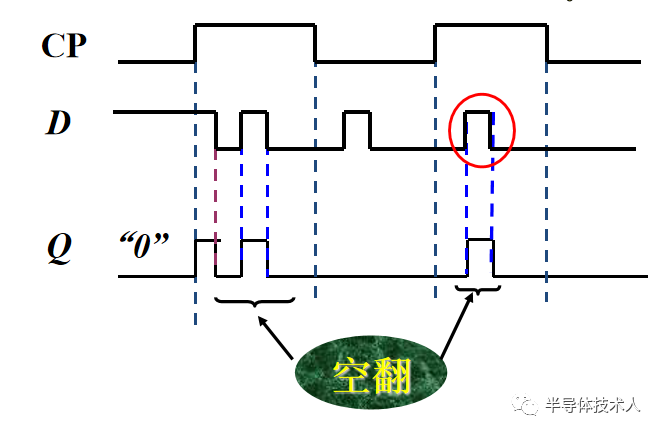

在CP=1期间,输出变化多于一次的现象,称为“空翻”。D锁存器的“空翻”现象,如何保证不出现“空翻”?

边沿触发器概念:

为了提高触发器的可靠性,增加抗干扰能力,希望触发器的次态仅取决于CP信号上升沿或者下降沿到达时刻输入信号的值。为此,研制了边沿型触发器。包括:维持-阻塞正边沿D触发器和利用CMOS传输门的主从型D触发器。

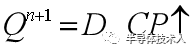

特性方程:

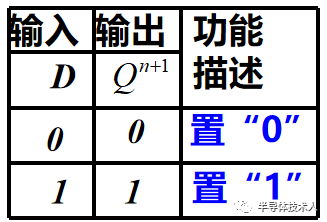

功能表

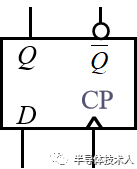

逻辑符号:

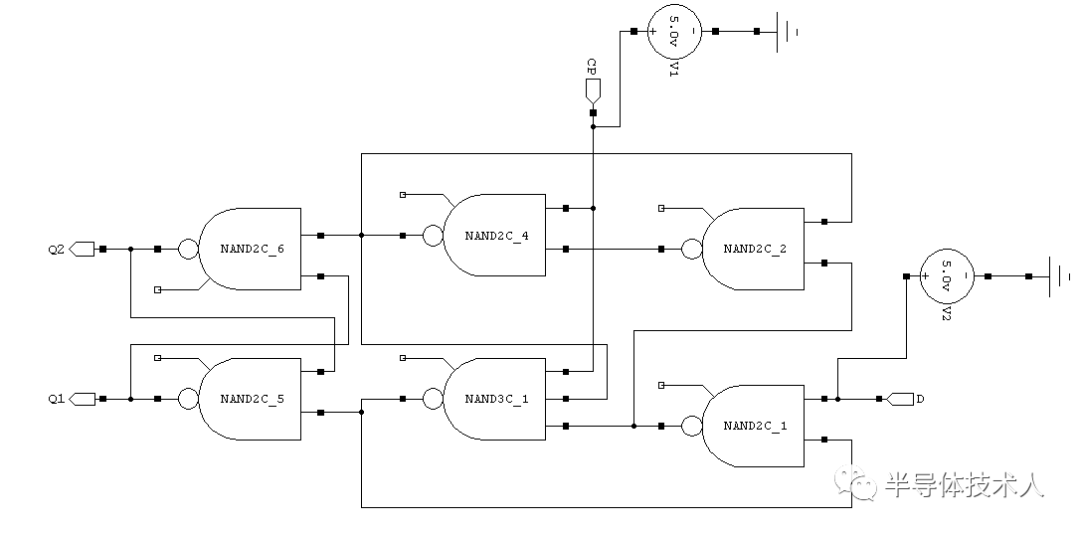

由钟控RS触发器与利用反馈构成的维持-阻塞电路组成:

D触发器设计:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY dflipflop IS

PORT (D,C : IN STD_LOGIC;

Q : OUT STD_LOGIC);

END dflipflop;

ARCHITECTURE Behavior OF dflipflop IS

BEGIN

PROCESS( C )

BEGIN

IF C'EVENT AND C='1' THEN

Q<=D;

END IF;

END PROCESS;

END Behavior;

使用Verilog HDL语言实现D触发器(带R、S端)

//门级

module cfq(s,r,d,clk,q,qbar);

input s,r,d,clk;

output q,qbar;

wire na1,na2,na3,na4;

nand

nand1(na1,s,na4,na2),

nand2(na2,r,na1,clk),

nand3(na3,na2,clk,na4),

nand4(na4,na3,r,d),

nand5(q,s,na2,qbar),

nand6(qbar,q,r,na3);

endmodule

或

//行为级

module dff_rs_async(clk,r,s,d,q);

input clk,r,s,d;

output q;

reg q;

always@(posedgeclk or posedge r or posedge s)

begin

if(r) q<=1'b0;

else if(s) q<=1'b1;

else q<=d;

end

endmodule

下一篇:时序分析基本概念介绍—时钟sdc