时间:2023-06-08 10:04

人气:

作者:admin

本文转自公众号,欢迎关注

未对齐导致问题案例 (qq.com)

前言

本文以一个实例,讲解RISC-V未对齐访问导致的问题.

未对齐导致的问题很常见,本文以实例分享调试分析过程。

过程

现象是程序进入了异常中断函数exception()

先分部打端点,结合step单步运行,确认执行哪个函数的哪一句执行后异常。

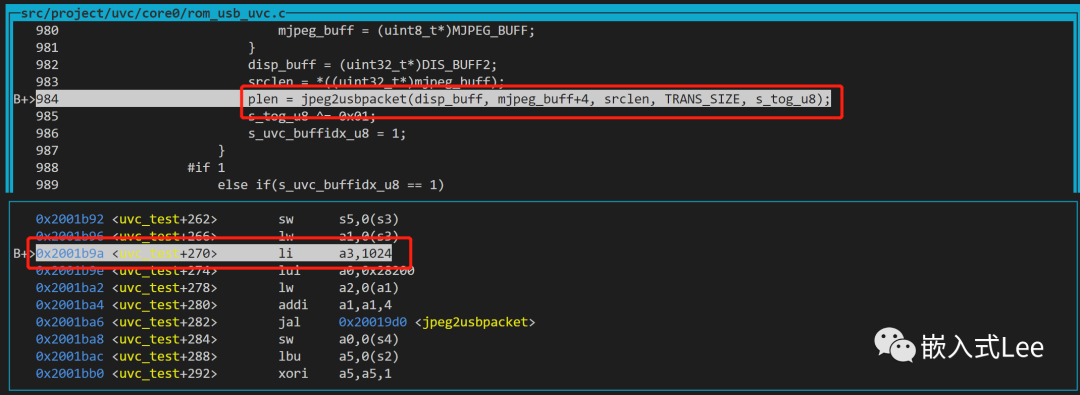

这里已经确认是rom_usb_uvc.c的984行执行后异常。

在执行异常的语句前打断点

b rom_usb_uvc.c:984

再重新运行到该处

显示汇编界面layout split

stepi按照汇编单步执行

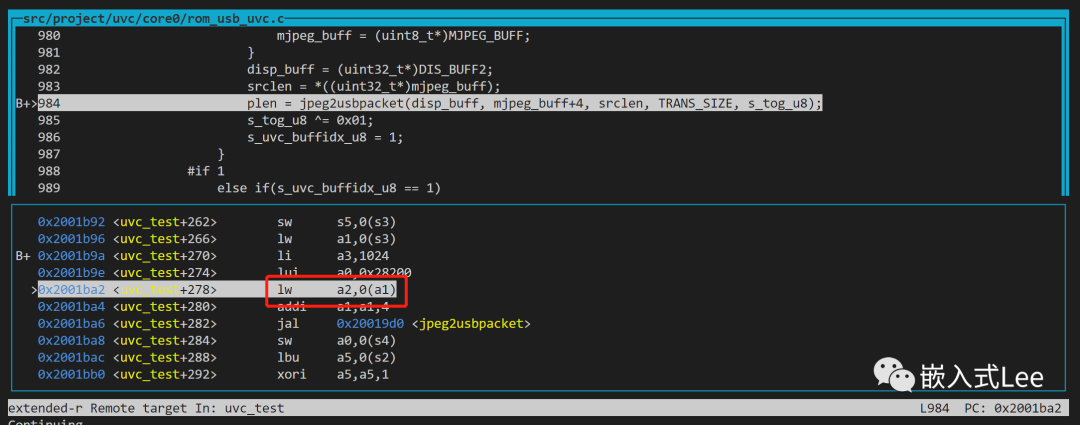

最终确认执行汇编指令

lw a2,0(a1)后异常

查看此时寄存器a1的值。

(gdb) info reg a1

a1 0x28429ddd 675454429

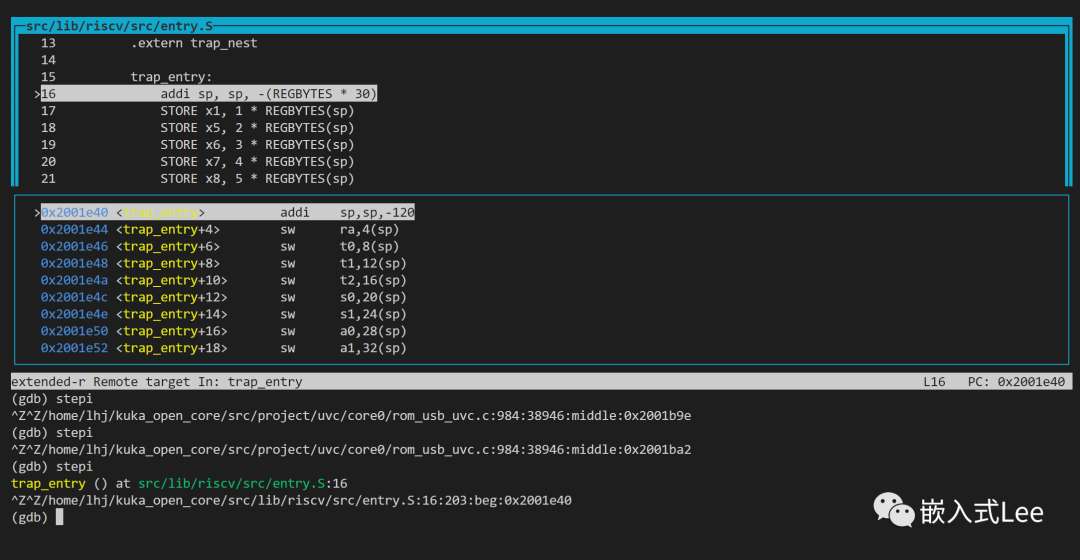

stepi执行完`lw a2,0(a1)``后进入异常处理函数

查看此时mcause寄存器

(gdb) info reg mcause

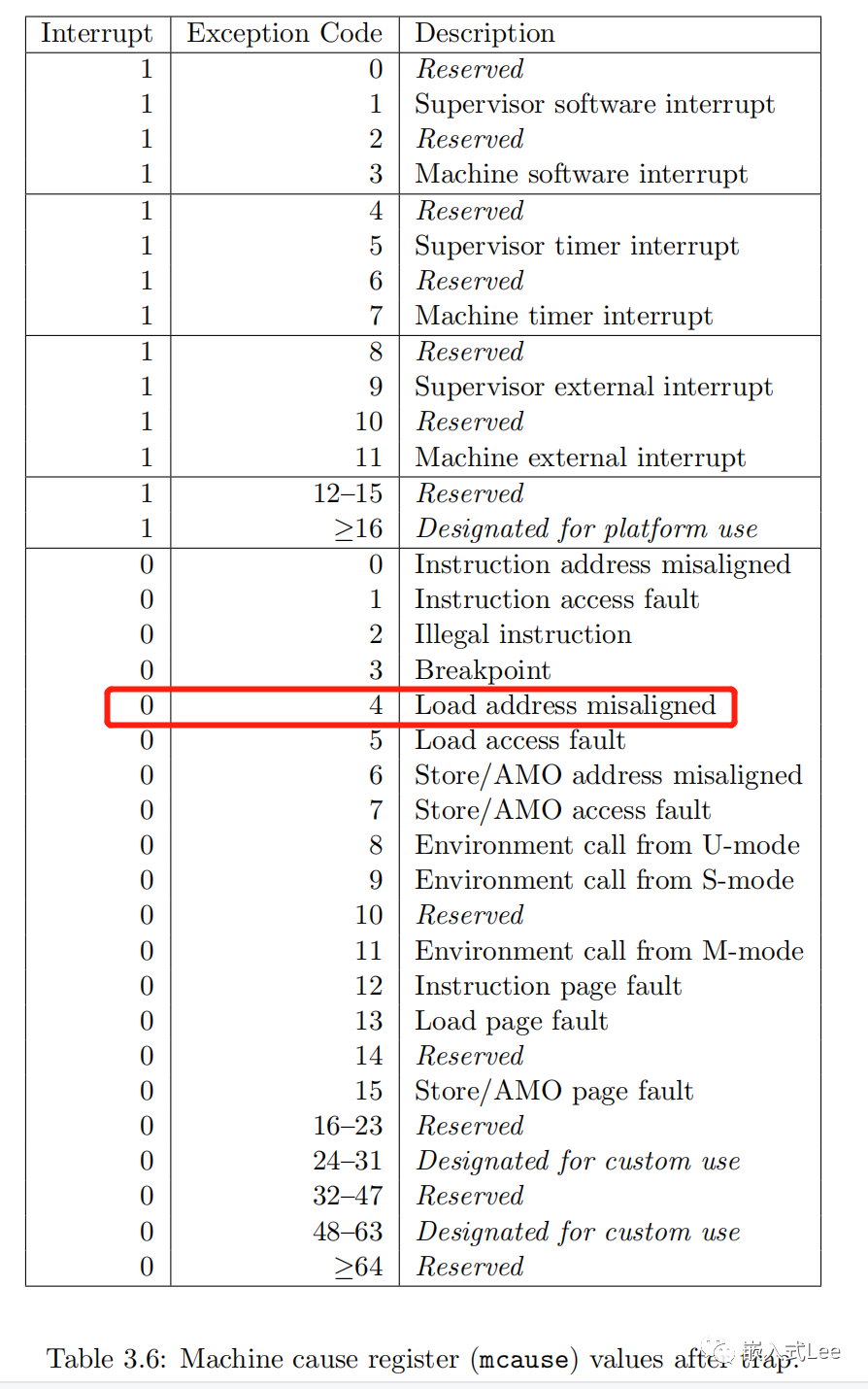

mcause 0x4 4

见 对应 即 所以修改缓冲区按照WORD对齐。<的<>.Load address misaligned。正是lw指令寄存器a1间接寻址非WORD对齐地址0x28429ddd导致。

jpeg2usbpacket函数传入的指向缓冲区的指针参数非WORD对齐导致。

审核编辑:汤梓红