时间:2023-06-05 16:24

人气:

作者:admin

上升沿检测电路

01

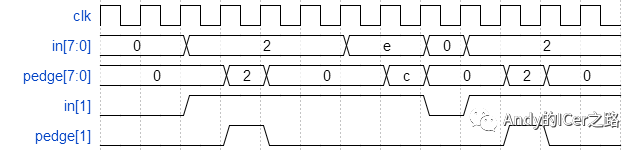

题目:对于8位向量中的每个位,检测输入信号何时从一个时钟周期的0变为下一个时钟周期的1(类似于上升沿检测)。应在从0到1的跳变发生后的周期内设置输出位。

以下为例子, 为了清楚起见,分别显示了in [1]和pedge [1]。

module top_module(

input clk,

input [7:0] in,

output reg [7:0] pedge);

reg [7:0] d_last;

always @(posedge clk) begin

d_last <= in;

pedge <= in & ~d_last; // A positive edge occurred if input was 0 and is now 1.

end

endmodule

第九行 d_last <= in ; 是记录信号in上一个cycle的状态;

第十行 pedge <= in & ~d_last; 检测上升沿,简答来说就是检测input由0变1。

双边沿检测电路

02

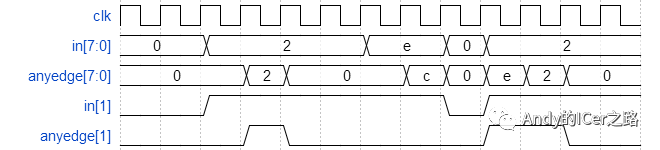

题目:对于8位向量中的每个位,检测输入信号何时从一个时钟周期更改为下一个时钟周期(检测任何边沿)。应在从0到1的跳变发生后的周期内设置输出位。

module top_module (

input clk,

input [7:0] in,

output [7:0] anyedge

);

reg [7:0] d_old;

always@(posedge clk)begin

d_old <= in;

anyedge <= d_old^in;

end

endmodule

第八行 d_old <= in ; 是记录信号in上一个cycle的状态;

第九行 anyedge <= d_old^ in ; 即现在的信号in与上一个状态不一样的话,输出1(异或是两个信号不一样置1),这样该电路就可以双边沿检测。