时间:2023-06-05 17:23

人气:

作者:admin

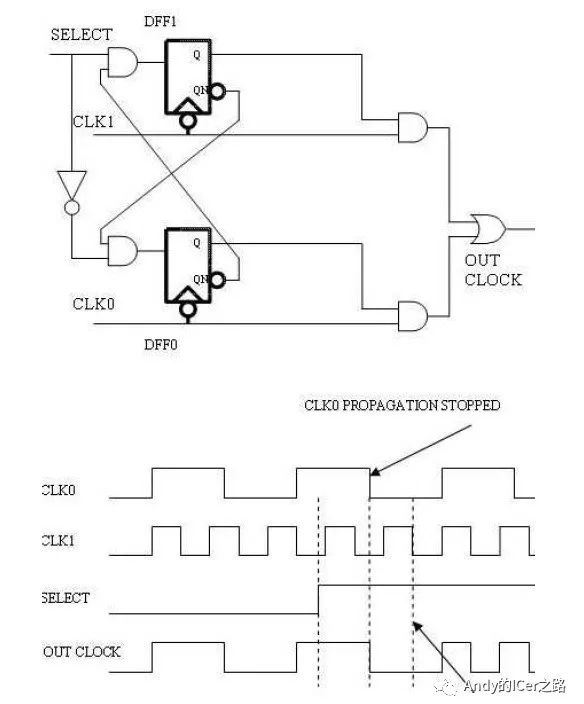

输入sel,clka,clkb,sel为1输出clka,sel为0输出clkb。

一、两个时钟源是倍数的关系

module Change_Clk_Source(

input clk1,

input clk0,

input select,

input rst_n,

output outclk

);

reg out1;

reg out0;

always @(negedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)

out1 <= 0;

else

out1 <= ~out0 & select;

end

always @(negedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)

out0 <= 0;

else

out0 <= ~select & ~out1;

end

assign outclk = (out1 & clk1) | (out0 & clk0);

endmodule

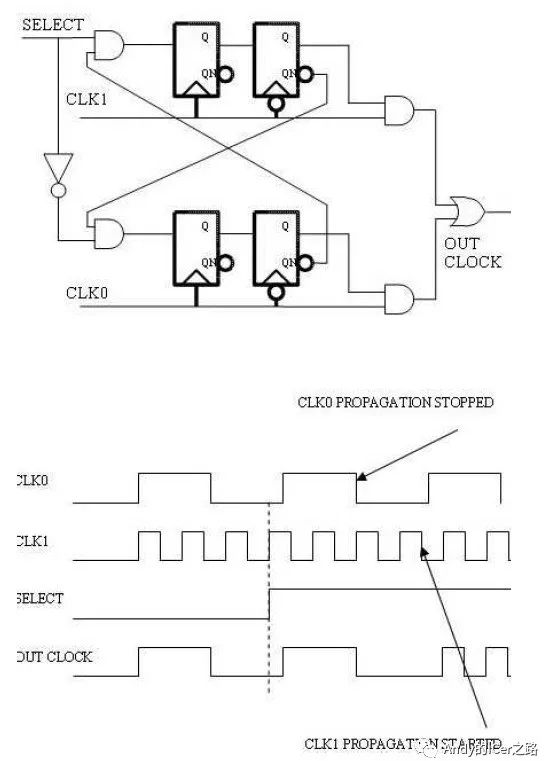

二、两个时钟源为异步时钟的关系

module Change_Clk_Source(

input clk1,

input clk0,

input select,

input rst_n,

output outclk

);

reg out_r1;

reg out1;

reg out_r0;

reg out0;

always @(posedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)

out_r1 <= 0;

else

out_r1 <= ~out0 & select;

end

always @(negedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)

out1 <= 0;

else

out1 <= out_r1;

end

always @(posedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)

out_r0 <= 0;

else

out_r0 <= ~select & ~out1;

end

always @(negedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)

out0 <= 0;

else

out0 <= out_r0;

end

assign outclk = (out1 & clk1) | (out0 & clk0);

endmodule