时间:2023-10-31 15:37

人气:

作者:admin

以AXI4为例,有AXI full/lite/stream之分。

在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种:

•AXI-Lite,AXI-Full以及AXI-Stream,其中AXI-Lite和AXI-Full都是基于memory map的形式实现数据传输(即包括地址总线),而AXI-Stream是以数据流的形式传输,无地址。

•其中AXI-Lite是AXI-Full的简化版,适合小批量的数据传输,常用来进行命令的传输,IP核的初始化等。

•AXI-Full则适用于大批量,高性能的数据传输。

AXI是一种用于传输数据的模块或总线,用于两个模块或多个模块之间相互传递数据。它本身有很多优点,被SOC广泛采用了。

AXI传输数据的过程

AXI-full传输数据是全双工的,也就是说,读写是同时进行的。

一条AXI总线有5条通道,两个用于读,三个用于写。

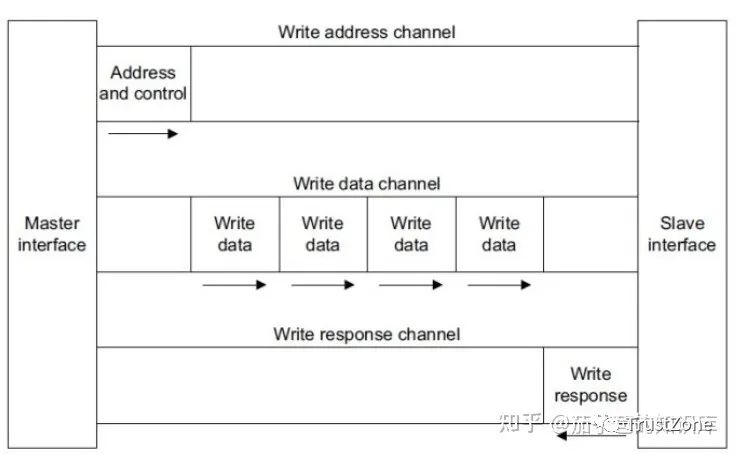

首先描述一下AXI的写数据过程:

(1)Master主机通过写地址通道将地址传给Slave从机,从机收到地址可通过写数据通道往里送入数据,写完之后通过写回应通道给主机一个结束信号。

(注:写回应通道只需2个bit位就能代表四种状态,传成功了,传失败的几种状态)

(注:写回复是针对整个传输操作(transcaction)的,而不是针对每个写入数据(data transfer))。

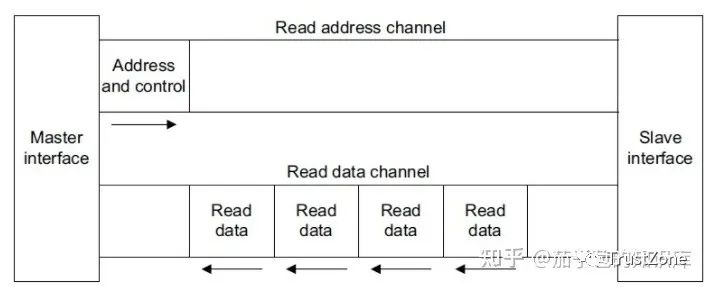

AXI读数据的过程:

主机给从机一个地址,从机通过读数据通道给主机返回数据。

为什么读只需要两个通道?因为完成信号可以用读数据传输一并传输。

从profibusDP转ModbusTCP,一网打尽转换技巧!