时间:2023-10-31 15:44

人气:

作者:admin

valid与ready信号分三种情况:

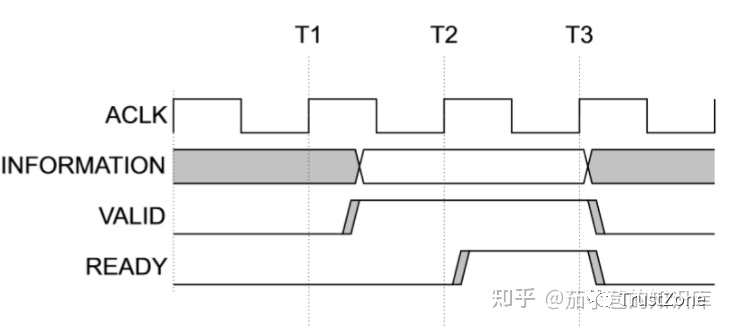

(1)valid信号先到达

主机valid信号早早就到了,T2时刻并没有见到接收方的ready信号。只能在T3时刻传输完成。

协议规定在这种情况下,valid信号一旦置起就不能置低,直到完成握手,至少传输一周期数据。 协议另外规定:发送方不能通过等待接收方 READY信号来确定置起 VALID 信号的时机。

通俗来讲就是设计发送方逻辑时,不能将 READY 信号作为置高 VALID 逻辑的条件,比如将 READY 信号通过组合逻辑生成 VALID信号,但接收方的ready信号按照协议可以依赖发送方的valid信号。

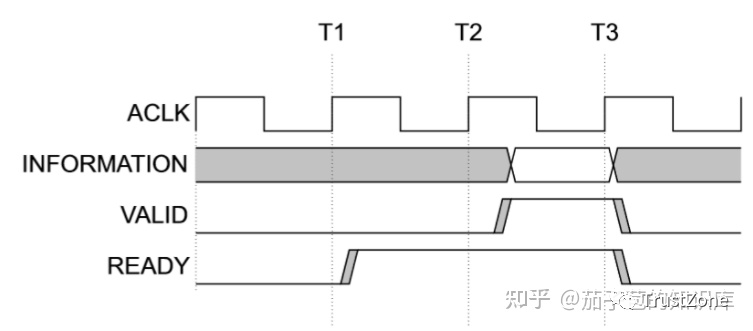

(2)ready信号先到达

ready信号很自由,可以等待valid信号到来之后再做响应,也可在valid信号到来前就置高,表示接收端已经做好准备。

而且,READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后置低 READY 信号。只要此时 VALID信号没有置起,这种操作是完全可以。

(3)tips

AXI总线是全双工的,全双工就意味着该总线的读写通道是分开的,互不影响,那就意味着每条通道都是单向传输,单向传输的通道就意味这两端节点的身份有差距,在AXI总线传输中,通道两端分为Master和Slave,主机总是发起读写请求的一方。

常见主机有CPU、DMA,而存储介质控制器则是典型的从机。主机可能通过从机读取或者写入存储介质。而显然从机不可能主动向 CPU 写入数据。

上一篇:AXI传输数据的过程

从profibusDP转ModbusTCP,一网打尽转换技巧!