时间:2022-09-16 15:54

人气:

作者:admin

1啥是IIC

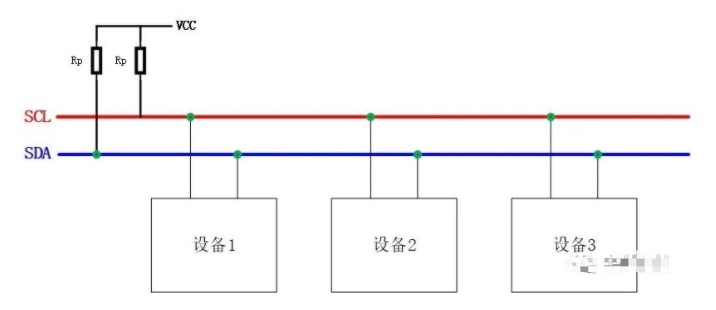

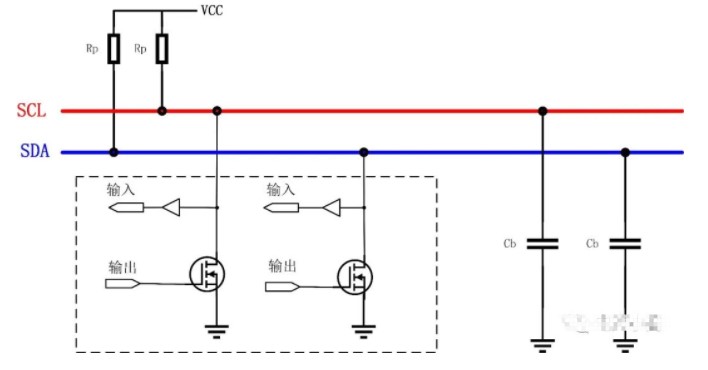

IIC(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的同步、半双工、串行总线。其信号线由时钟(SCL)和数据(SDA)两条线组成。网络结构如下图。

2IIC如何工作

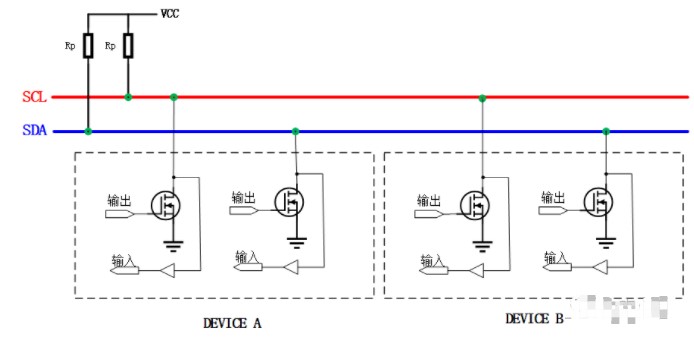

挂载在IIC总线上的设备既可以作为主机也可以作为从机。既可以发送数据也可以接收数据。但是同一时刻,只能有两个设备进行通信,并且只能一个发送,另一个接收,即半双工通信。如何实现此特性呢?秘密就在设备的总线端口上,请看下图。

如上图所示:

IIC总线的时钟和数据信号线,输出端是漏极开路(OD门)或者集电极开路(OC门),因此只能输出逻辑低(0)和高阻态(Hiz)。为了输出逻辑高(1),必须上拉电阻到电源。在数字电路上,此设计称为:线与逻辑。

线与逻辑:两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。

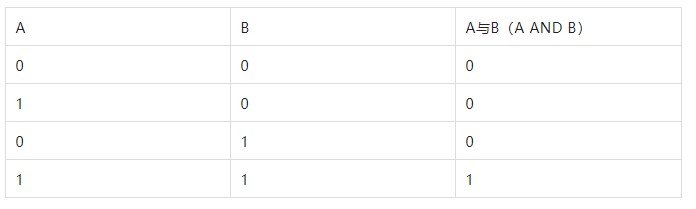

与逻辑:只要参与运算的单元有一个是0,其结果为0

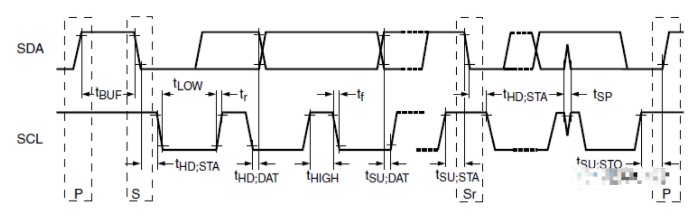

因此IIC总线协议规定:

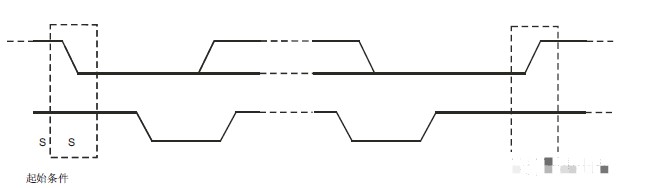

SDA和SCL同时为高电平时,总线为空闲状态;

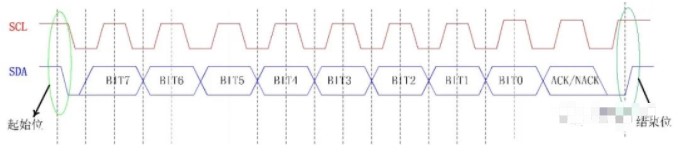

SCL为高电平期间,SDA由高电平变为低电平(下降沿),为起始信号;

SCL为高电平期间,SDA由低电平变为高电平(上升沿),为结束信号;

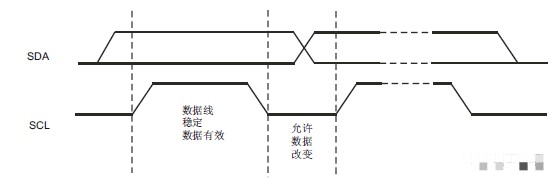

传输数据时,SCL低电平数据进行传输,高电平保持;

IIC一般采用MSB(Most Significant Bit)传输方式;

一般总线上数据都以字节Byte(8 bit)传输,第9bit为应答位;

应答ACK为低电平,NACK为高电平;

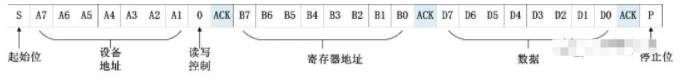

一个典型的IIC数据帧

3IIC总线竞争机制

上文中说到:总线中的设备既可以做主机也可以做从机,那么谁做主机?谁做从机?

这是两个问题,一般情况下主机提供时钟SCL,发送数据给从机,从机响应。

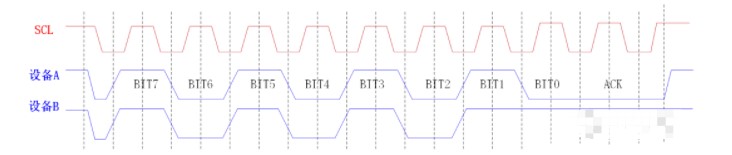

Q1:如果有两个或者以上的设备同时想发送数据怎么办?

这就是涉及到总线的仲裁机制。因为总线上只能有一个主机和一个从机同时工作。举例说明总线竞争机制。假设设备A和设备B同时向总线发送数据,设备A发送8b'1010_1010,设备B发送8b'1010_1110,当发送到BIT2的时候,A发送的是0,B 发送的是1,这时候总线状态为0,因此B退出竞争,释放总线。

从上面可以看出:谁最先发送0,谁获得总线控制权。

4IIC通信协议Q2:哪个从机响应?如何响应?

分析此问题必须从协议层入手,找谁的问题很好解决,就是设备编号的问题,专业的叫做设备地址. 显而易见的,总线上的设备地址必须是唯一的。为了实现互联互通,协议规定:设备地址有7bit或10bit,常用7bit地址,理论上最大支持128(2^7)个设备。

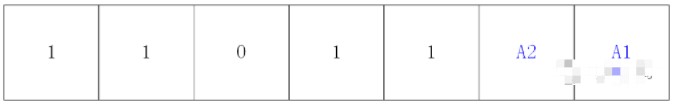

一般为了使用方便,设备地址的最后几位使用硬件设置,便于同一个系统中使用相同的器件。典型的就是立体声扬声器功放。例如TFA9879设备地址为:

那么,有效的地址为{7b'1101100, 7b'1101101, 7b'1101110, 7b'1101111},也就是说同一个总线上最多可以使用4颗此芯片。

IIC总线常用于内存读写以及寄存器配置,因此本文以EEPROM 24C02读写时序为例。其他类型芯片方式类似。

单字节写时序

1、主机发送起始位

2、主机发送从机地址,读写控制位是0,表示写

3、从机应答ACK

4、主机发送寄存器地址

5、从机应答ACK

6、主机发送数据

7、从机应答ACK

8、主机发送停止位,总线挂起

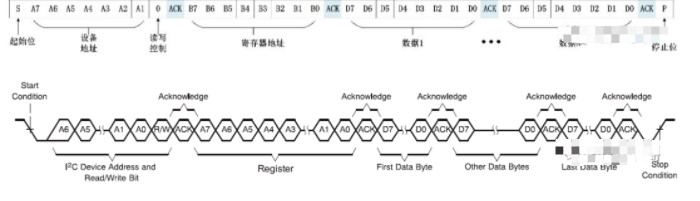

多字节写时序

1、主机发送起始位

2、主机发送从机地址,读写控制位是1,表示写

3、从机应答ACK

4、主机发送寄存器地址

5、从机应答ACK

6、主机写第一个数据

7、从机应答ACK

8、主机写第N个数据

9、从机应答ACK

10、主机发送停止位,总线挂起

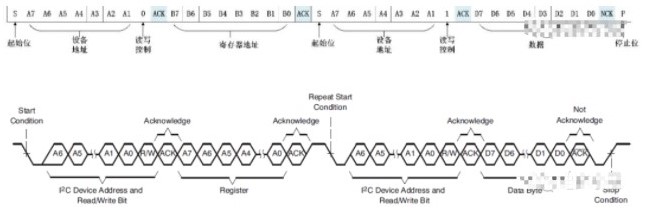

单字节读时序

1、主机发送起始位

2、主机发送从机地址,读写控制位是0,表示写

3、从机应答ACK

4、主机发送寄存器地址

5、从机应答ACK

6、主机又发送起始位

7、主机发送从机地址,读写控制位是1,表示读

8、从机应答ACK

9、从机发送数据

10、主机应答NACK

11、主机发送停止位,释放总线

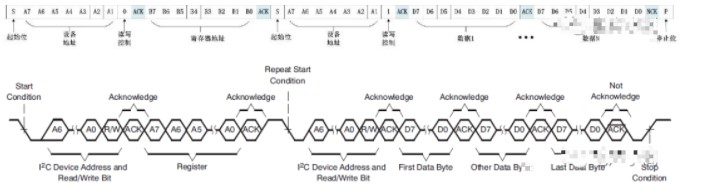

多字节读时序

主机发送起始位

主机发送从机地址,读写控制位是0,表示写

从机应答ACK

主机发送寄存器地址

从机应答ACK

主机又发送起始位

主机发送从机地址,读写控制位是1,表示读

从机应答ACK

从机发送数据

主机应答ACK

从机发送数据N

主机应答NACK

主机发送停止位,总线挂起

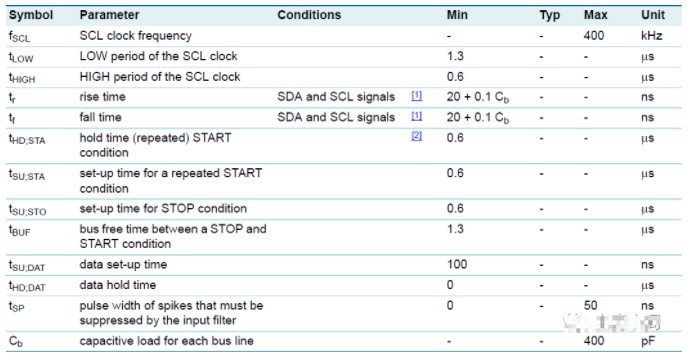

5IIC电气特性

按照传输速率,IIC被分类为:

标准模式(Standard Mode):100K bps

快速模式(Fast Mode):400K bps

超快速(Fast Mode Plus) : 1 M bps

高速模式(High Speed Mode):3.4M bps

以TFA9879为例,简要说明一下IIC电气要求:

时钟频率最大400kHz

时钟高电平和低电平时间,一般情况下,tLOW /tHIGH = 2:1

tHD;STA:起始信号保持时间,最小0.6us

tSU;STA: 起始信号建立时间,最小0.6us

tSU;STO: 结束信号建立时间,最小0.6us

tSU;DATA: 数据建立时间,最小100ns

tHD;DATA: 数据保持时间,无要求

tBUF:总线空闲时间,最小1.3us

tSP:毛刺信号,最大宽度50ns

容性负载:最大400pF

上拉电阻如何选型?

考虑两个核心问题

1功耗

2速度

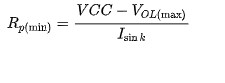

功耗决定上拉电阻的下限(最小值):

当输出为0时候,电源VCC通过上拉电阻Rp,经过MOS管到地,一般MOS管导通电阻很小,可以忽略。一般情况下,芯片中MOS管导通时能承载的电流可以参考手册,常见2 ~ 4mA。

IIC协议规定:低电平最大电压0.4V,那么

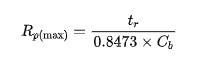

速度决定了上拉电阻的上限(最大值):

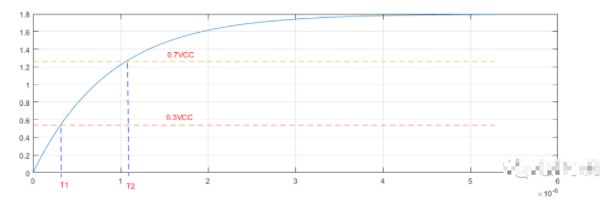

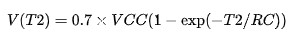

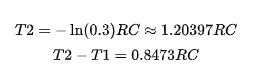

IIC的高电平是由上拉提供的,线路由于寄生电容Cb的影响,导致上升沿变缓,因此上升沿时间决定了上拉电阻的上限值。一般地,选择高电平为70%VCC,低电平为30%VCC,RC电路零状态响应曲线如下图:

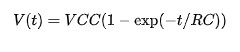

根据时间常数计算公式:

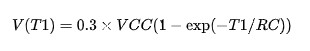

低电平时刻T1

那么,

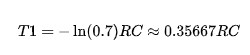

高电平时刻

那么,

因此

从profibusDP转ModbusTCP,一网打尽转换技巧!