时间:2020-09-23 11:18

人气:

作者:admin

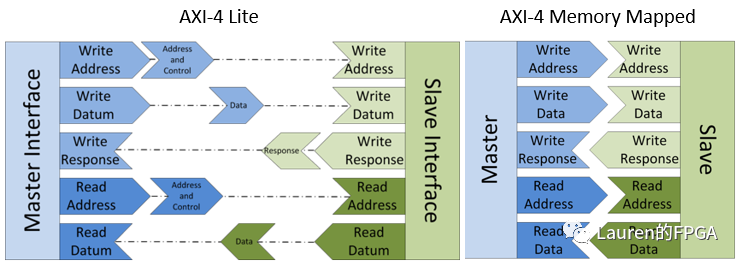

AXI-4 Lite可以看作是AXI-4 Memory Mapped的子集,从下面的示例图中就可见一斑。最直接的体现是AXI-4 Lite的突发长度是固定值1。

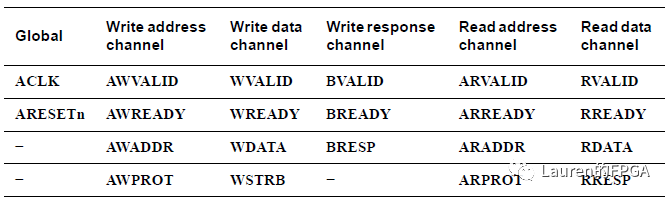

AXI-4 Lite的接口信号如下图所示。同样都是5个独立通道,但由于突发长度被限制为1,使得某些信号不再需要,例如ARLEN和AWLEN就不再需要了,因为两者均为0,同时用于显示突发类型(Burst Type)的ARBURST和AWBURST、表明一笔数据交易的最后一个有效数据WLAST和RLAST均不再需要了。此外,AXI-4 Lite要求数据位宽必须是32-bit或64-bit,故ARSIZE和AWSIZE也不再需要了。

就数据传输机制而言,AXI-4 Lite和AXI-4 Memory Mapped是一致的,每个通道都有相应的VALID和READY信号对。

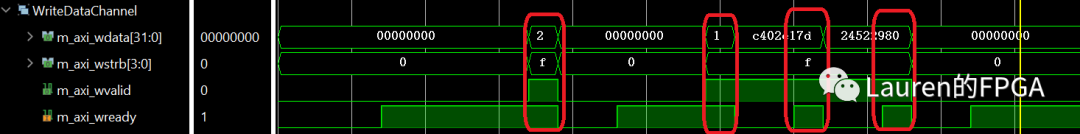

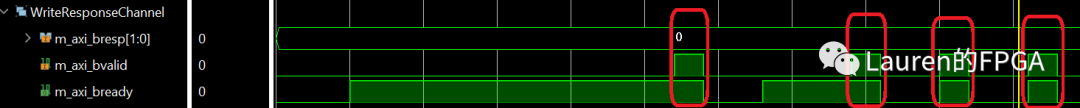

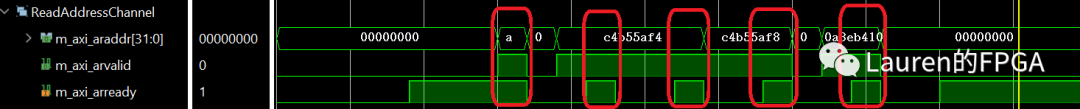

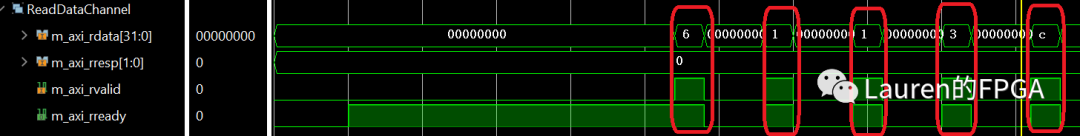

这里我们给出一个仿真波形供大家参考,以便理解AXI-4 Lite接口协议。

写地址通道

写数据通道

写响应通道

读地址通道

读数据通道

上一篇:dp接口应用特点分析

下一篇:AXI4接口协议的基础知识

从profibusDP转ModbusTCP,一网打尽转换技巧!