时间:2025-02-24 10:10

人气:

作者:admin

之前的文章介绍过DAC几种结构和开关切换策略,但在实际应用中,其性能受到电容阵列的匹配影响,此时需要引入校准技术来优化这一问题。

背景

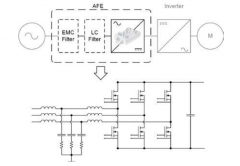

首先使用巨霖的通用电路仿真工具PowerExpert画出SARADC中DAC+比较器的理想模型:

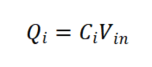

由上图所示,前半部分是电容阵列,比较器后是数据寄存器,用来存放每一次比较器数输出的数字码,并送回电容阵列控制开关的切换。在采样阶段电容阵列开关分别接输入信号Vin,此时阵列中每个电容上储存的电荷为:

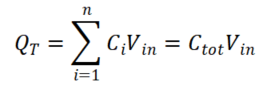

所有电容存储的电荷量之和为:

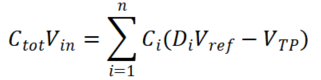

在比较阶段转换电容下极板到VrefP/N,通过电荷守恒方程可得:

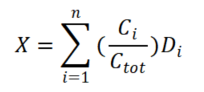

上式 为电容的上极板电压,由此可知,输出码等于:

为电容的上极板电压,由此可知,输出码等于:

在理想情况下,电容阵列从LSB开始按照二进制加权递增, 应是精准的二进制值,然而在实际工艺中,电容值会存在失配,导致权重

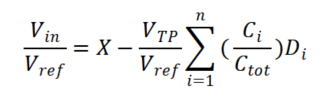

应是精准的二进制值,然而在实际工艺中,电容值会存在失配,导致权重 偏离理想值,此时输入电压与输出数字码关系为:

偏离理想值,此时输入电压与输出数字码关系为:

此现象在180nm及以下工艺中更加明显。此时就需要一种校准方式解决此问题,通过传统引入冗余位设计虽然可以避免失配,但是会增加转换位数从而增加功耗和比较时间,通过注入校正电荷校准则需要高精度的DAC电路,难以实现且会占用额外面积。

原理

下面介绍一种名为Split ADC的架构来优化上述问题,该架构将一个SARADC“分裂”成两个,称为通道A和通道B,两个阵列分配从LSB位到MSB位的电容。通过后续动态分配模块实现将比较器决策分配给不同电容段,权重模块将后续校准电路校准后的权重 与动态分配模块产生的决策

与动态分配模块产生的决策 相乘,然后将上下两通道的相乘结果

相乘,然后将上下两通道的相乘结果 取差模

取差模 送入后续误差比较器,再取共模

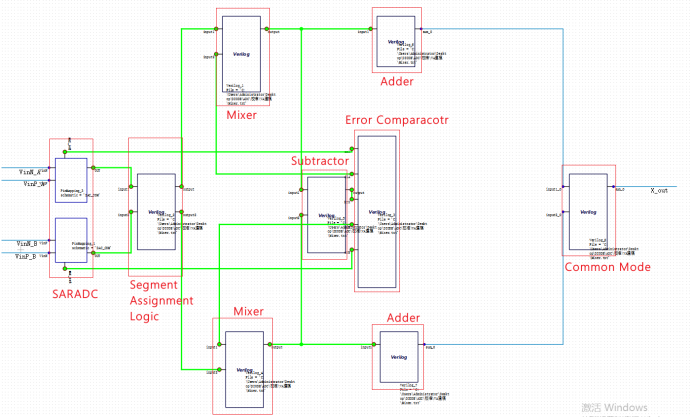

送入后续误差比较器,再取共模 输出以抑制随机噪声。以一个16位高精度的SARADC为例,原理图如下所示:

输出以抑制随机噪声。以一个16位高精度的SARADC为例,原理图如下所示:

动态分配模块

将两个SAR决策逻辑序列 的输出接到一个动态分配模块,该模块是使用一个4位的LFSR实现,每个转换周期更新一个值,生成新的PRN值。在传统无校准的结构中,每一个电容段只会对应一个权重,如果这个电容段出现了失配,那么输出结果将会出现偏差,而动态分配模块的作用是随机改变电容段和SAR决策逻辑序列

的输出接到一个动态分配模块,该模块是使用一个4位的LFSR实现,每个转换周期更新一个值,生成新的PRN值。在传统无校准的结构中,每一个电容段只会对应一个权重,如果这个电容段出现了失配,那么输出结果将会出现偏差,而动态分配模块的作用是随机改变电容段和SAR决策逻辑序列 的映射关系,避免输入信号长期维持在一个模拟量导致某些位的输出数字量无法被校准。可以使用Verilog编写动态分配模块并导入PowerExpert中。

的映射关系,避免输入信号长期维持在一个模拟量导致某些位的输出数字量无法被校准。可以使用Verilog编写动态分配模块并导入PowerExpert中。

误差比较模块

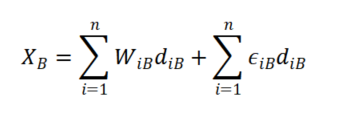

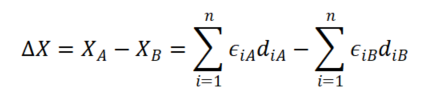

误差比较模块将AB两个通道的差模输出作为输入,其中A通道的输出为以下表达式:

前项表示理想权重下的输出,后项表示误差,同理B通道的输出如下:

误差比较器得到的输入为:

上式在实际电路设计中还需要考虑两个通道的输入信号偏移和增益误差,此处忽略。误差比较器的目的就是通过调整 使得

使得 等于零,从而使AB两通道的差模输出为0。具体实现是通过LMS算法迭代来逐渐修正

等于零,从而使AB两通道的差模输出为0。具体实现是通过LMS算法迭代来逐渐修正 ,下面简单举例介绍LMS算法原理和在误差比较器里面的运用。

,下面简单举例介绍LMS算法原理和在误差比较器里面的运用。

假设第五个电容段存在失配,同时也被激活 ,那么子通道A的权重由实际权重0.5变为了

,那么子通道A的权重由实际权重0.5变为了 ,误差项

,误差项 被送到了

被送到了 中,LMS算法检测到

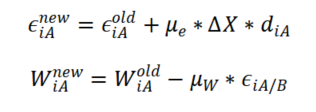

中,LMS算法检测到 ,于是进行以下迭代:

,于是进行以下迭代:

都是步长参数,用来控制收敛速度。

都是步长参数,用来控制收敛速度。  后将迭代的

后将迭代的 新权重结果送入乘法器中与电容阵列决策

新权重结果送入乘法器中与电容阵列决策 相乘,得到校准后的结果。在实际电路设计中,为了高效估计误差参数,会根据多次收集的

相乘,得到校准后的结果。在实际电路设计中,为了高效估计误差参数,会根据多次收集的 和电容阵列激活信号构建矩阵方程,再使用最小二乘法求解已优化误差参数估计,从而减小功耗,有兴趣的读者可以自行了解。

和电容阵列激活信号构建矩阵方程,再使用最小二乘法求解已优化误差参数估计,从而减小功耗,有兴趣的读者可以自行了解。

仿真

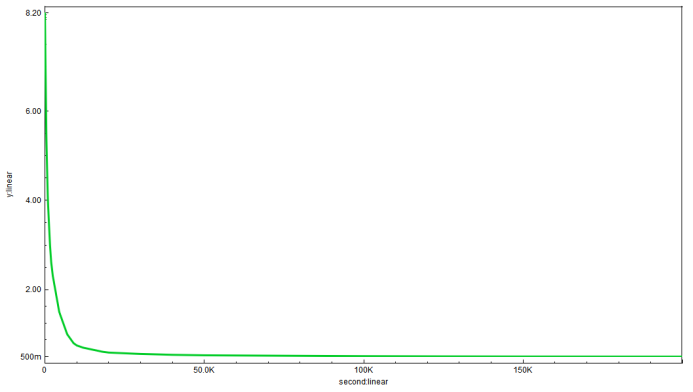

手动在电容阵列中添加10%的误差,从下面仿真得出的波形可以看出,输出X_out被逐渐缩小,最终稳定在理想权重0.5。

欢迎从官网申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!

龙腾半导体SGT MOSFET LSGT085R018在智慧农业无