时间:2023-09-11 09:32

人气:

作者:admin

NAND闪存工艺

闪存芯片是非挥发存储芯片,广泛用于电子产品,特别是如数码相机、MP3播放器、手机、全球定位系统(GPS)、高端笔记本电脑和平板电脑等移动电子产品的存储应用。与磁性硬盘存储器相比,闪存的数据存取时间短,消耗的功率较少,而且因为没有任何移动部件,所以可靠性更高。

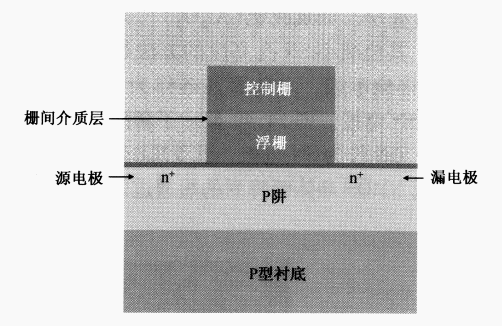

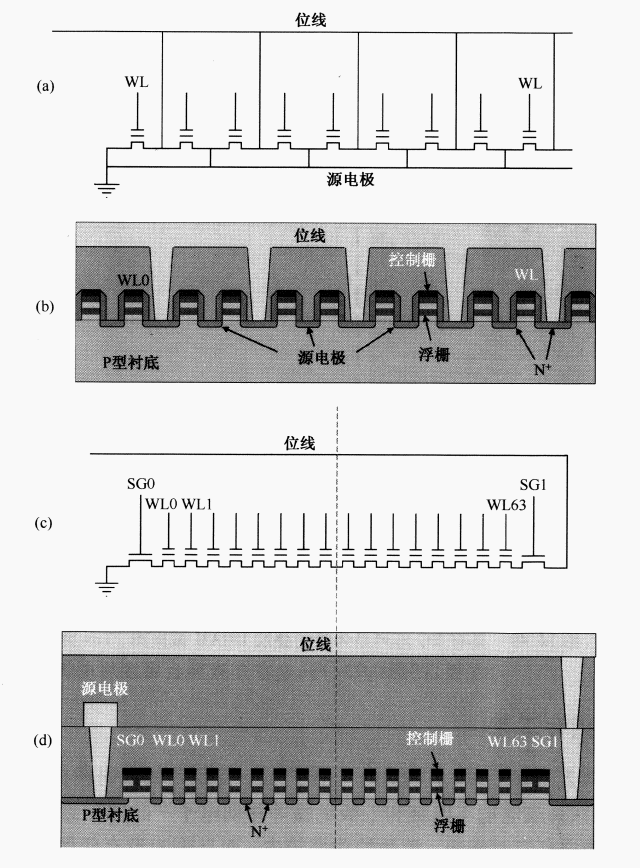

所有市场上的闪存芯片都是基于浮栅结构的电荷俘获器件,这种结构已经在后面的部分讨论过。下图显示了浮栅器件结构,这种结构与NMOS类似。根据不同的电路结构,有两种类型的闪存器件——NAND和NOR(见下图)。

下图(a)和(b)分别显示了NOR闪存电路和横截面示意图。下图(c)和(d)为64位NAND快闪存储电路和相应的截面图。可以看出,一个NOR闪存等效于1位字符NAND快闪存储器,这种结构不需要选择栅。虽然NOR闪存比NAND快闪存储器的读取时间短,然而它具有更长的写入时间和擦除时间。由于低的封装密度,NOR闪存比NAND快闪存储器价格高。大多数快闪存储器芯片是NAND芯片,本节只讨论NAND快闪存储器的工艺流程。

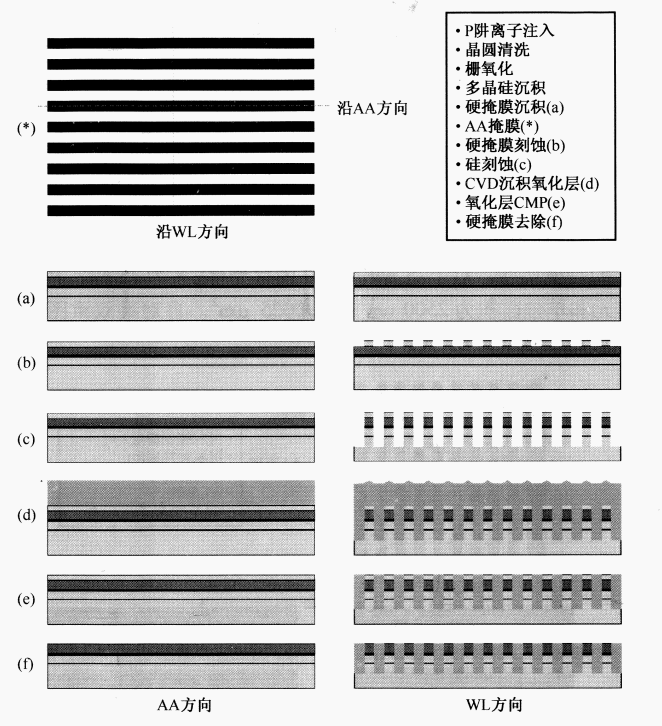

下图显示了自对准浅沟槽隔离(SA-STI)工艺流程。P阱离子注入后,生长栅氧化层并利用硬掩膜层沉积浮栅,使用AA版图图形化硬掩膜,然后刻蚀浮栅、栅氧化层和硅衬底形成AA图形化。氮化硅或氮氧化硅是最常使用的硬掩膜材料,多晶硅是最常使用的浮栅材料。硅沟槽刻蚀后,使用高密度等离子体CVD沉积氧化层填充沟槽,利用CMP工艺去除氧化物并停止于硬掩膜层。最后通过剥离工艺去除硬掩膜后完成SA-STI过程。

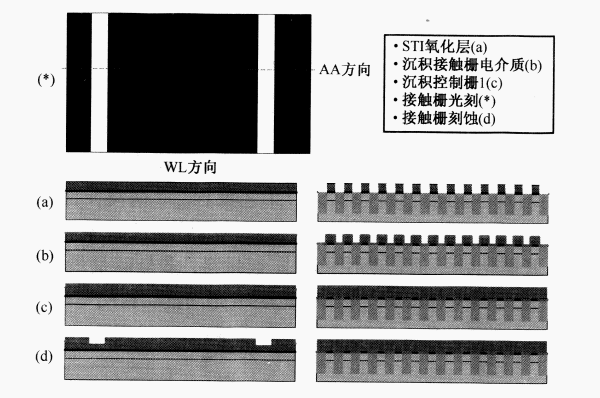

下图显示了内部栅接触的工艺过程。这是浮栅NVM器件特有的工艺,因为选择栅MOSFET及外围区域的控制电路没有浮栅器件,需要内部栅将浮栅层和控制栅层连接起来。一般情况下浮栅利用多晶硅制成,内部栅介质是氧化物-氮化物-氧化物(oNo)叠层结构,控制栅的第一层也是多晶硅,第二层通常是金属,如硅化钨或钨等。下图(a)所示的STI氧化物可以使得控制栅和浮栅同步增加,当特征尺寸不断缩小时,这种情况是不可避免的。

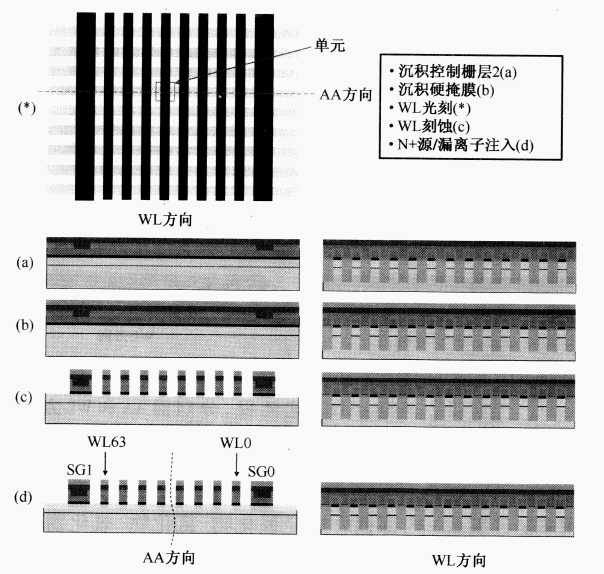

在下面的图中非常详细的显示了WL工艺流程。通过连接浮栅和控制栅的内部栅接触沉积金属,所有的MOSFET栅极位于外围区域。WL层的密集线/图形间距具有IC产品最高的集成度。在下面的图中所示AA版图中的方块NAND快闪存储器单元区域可以表示为4F2,F表示结构的最小特征尺寸,4F2是可以达到的最高图形密度。对于NAND快闪存储器,AA和WL线/间距比为1:1,因此F是AA和WL的特征尺寸对于25nmNAND闪存器件,F为25nm,其中AA和WL的CD为25nm,存储单元和单位面积为2500nm或0.0025um2。自对准双重图形技术适用于图形化WL层,也可以应用于AA和BL层。

审核编辑:刘清

龙腾半导体SGT MOSFET LSGT085R018在智慧农业无