时间:2023-03-30 10:12

人气:

作者:admin

LLC转换器凭借简单、高效的优点而成为广泛用于PC、服务器和电视电源的拓扑结构。其谐振操作可实现全负载范围的软开关,从而成为高频和高功率密度设计的理想选择。此外,LLC转换器采用电容滤波器,无需输出滤波电感。有了电容滤波器,LLC转换器还可以使用额定电压较低的整流器,从而降低系统成本。此外,次级侧整流器可实现零电流转换,大大减少了反向恢复损耗。利用LLC拓扑结构的各项优势,可进一步提高效率,降低输出整流器的损耗。

用于LLC谐振转换器的同步整流器

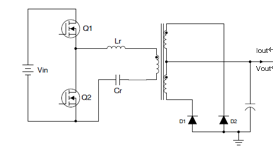

使用二极管整流器时,如图1所示,全部输出电流流过输出二极管。对于低电压或高输出电流应用,这些二极管整流器中存在显著的效率损失和热应力。

图1.带二极管整流器的LLC转换器

如果二极管用固定的正向电压降VF建模,则可以基于等式1估计每个整流二极管的损耗。,采取这样的方式计算,对于具有0.5V正向压降的12V,10A输出设计来说,每个二极管产生2.5W的损耗,这意味着总效率损失约为4%。

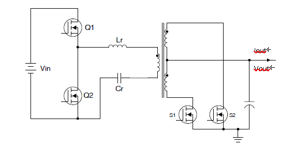

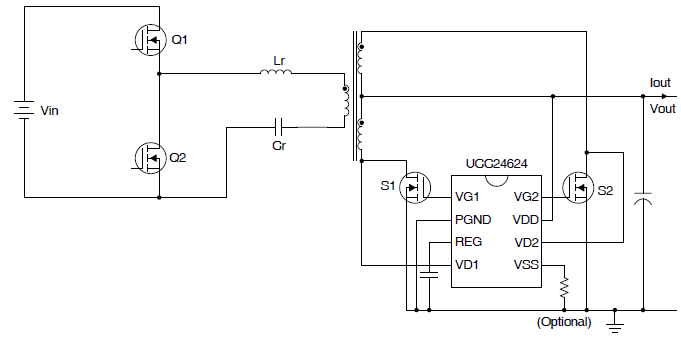

使用如图2所示的同步整流器(SR),MOSFET上的电压降可能远低于典型的二极管正向电压。

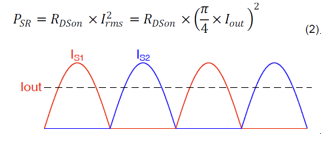

对于相同的设计,如果用MOSFET替换整流二极管,并通过适当的控制,可以使用公式2计算传导损耗,次级侧电流形状与图3所示的正弦曲线类似。使用4 mΩ RDSon,每个整流器损耗可降至0.247 W,相当于总效率损失0.4%。

图2.带同步整流器的LLC转换器

图3.LLC次级侧电流

LLC同步整流器控制的设计挑战

可以通过监测其漏极-源极电压(VDS)来控制同步整流器。在同步整流器导通之前,电流流过其体二极管。体二极管正向电压降可用于触发同步整流器导通。在同步整流器导通后,其导通电阻变为电流检测电阻,VDS可用于在电流反转之前检测电流以关断同步整流器。尽管控制方法非常简单,但LLC谐振转换器同步整流器控制仍存在一些设计挑战。

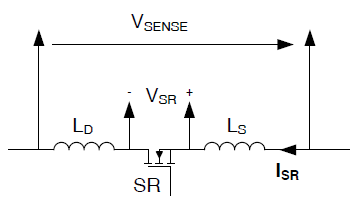

同步整流器关断时间:LLC同步整流器控制的最大挑战是在正确的时间关断同步整流器。与反激式转换器不同,LLC同步整流器通常承载更高的电流并具有更高的di/dt。如图4所示,检测电压VSENSE用于同步整流器控制。

它包括RDSon压降(VSR)和由di/dt引起的封装电感(LD,LS)上的偏移电压。对于高di/dt和封装电感,该偏移电压可能很大并且同步整流器经常过早关断,这导致较长的体二极管导通时间和较大的传导损耗。

图4.同步整流器控制器检测到的电压

突发模式运行:与LLC转换器中使用的同步整流器相关的另一个挑战是突发模式运行。在突发模式期间,两个初级侧开关都将关断。开关节点电容器与LLC变压器磁化电感器谐振。这种低频寄生振荡有潜在的可能使同步整流器错误地导通并使输出将能量传递到初级侧,这将导致更多的传导损耗。

低待机功率:即使同步整流器节省了传导损耗,由于控制电路和栅极驱动器损耗,它们也会给系统增加额外的损耗。由于节省了大量传导损耗,因此在较重负载下这种额外损耗微不足道。但是,在空载条件下,将SR控制器置于待机模式并使用SR体二极管进行整流,可以高效地禁用SR控制器。

可靠性问题:由于电容滤波器的存在,如果两个同步整流器同时导通,则输出将通过变压器短路,并且预计会发生灾难性故障。防止两个同步整流器同时导通至关重要,甚至应该考虑到由电路噪声引起的错误触发。

用于LLC转换器的UCC24624同步整流器控制器

为了实现更好的LLC谐振转换器效率,可引入UCC24624双同步整流器控制器与LLC控制器(如UCC25360系列)一起使用。UCC24624实现了同步整流器控制的VDS检测,以及针对LLC同步整流器控制挑战的各种功能,使其成为实现高效LLC设计的理想解决方案。

为解决同步整流器提前关断的挑战,UCC24624实现了比例栅极驱动,以及可调节的+ 10.5 mV关断阈值。比例栅极驱动在电流下降沿降低同步整流器栅极电压。降低的栅极驱动电压会增加同步整流器MOSFET RDSon,从而导致同步整流器上的压降更高。这种增加的压降超过了封装电感引起的偏移电压。加上正关断阈值,UCC24624可将体二极管导通时间降至最低。为了使具有更高寄生电感的封装(例如TO-220)更好地工作,通过使用从VSS引脚到同步整流器MOSFET源极引脚的外部偏移电阻,UCC24624可让设计人员进一步提高其关断阈值。这使得控制器更少受到MOSFET封装的影响。

图5.用于LLC转换器的UCC24624双同步整流器控制器

为了改善突发模式运行,除了传统的停机消隐的方式外,UCC24624还采用自适应导通延迟时间。在正常运行期间,导通延迟保持很短,从而缩短体二极管导通时间并提高效率。在突发模式运行期间,同步整流器运行从互补方式变为无转换方式。UCC24624可通过这一指示检测LLC是否已进入突发模式运行。这可增加导通延迟时间,有助于抑制寄生振荡。在轻负载条件下,为提供额外的噪声抑制,导通延迟也会增加。自适应导通延迟时间的这一性能,有助于在不牺牲效率性能的情况下抑制噪声。

UCC24624还具有内置的自动待机模式检测电路,而无需使用外部元件。对于空载时的LLC转换器,转换器以突发模式运行以调节输出电压。每个开关周期中的LLC同步整流器导通时间仍然很长,而转换器的平均开关频率非常低。UCC24624根据转换器平均开关频率检测轻载条件。它可使控制器在空载时进入待机模式,有助于实现低待机功耗。

为了提高可靠性并防止两个同步整流器同时导通,将互锁逻辑应用于同步整流器控制的两个通道。在一个通道处于同步整流器导通时间期间,同时禁止另一个通道同步整流器导通。即使在系统噪声的干扰下,互锁逻辑仍可提高运行的可靠性。

总结

凭借所有内置智能以及TI UCC25630系列LLC控制器,UCC24624为LLC转换器设计中的同步整流器控制提供了高效、经济的解决方案。

审核编辑:郭婷

上一篇:干式变压器声音异常有哪些原因

龙腾半导体SGT MOSFET LSGT085R018在智慧农业无