时间:2023-09-06 09:39

人气:

作者:admin

0前言

本文为EMC小知识学习简笔系列的第三篇,前文EMC小知识学习简笔(二)介绍了EMC三要素、插入损耗及电源滤波相关案例,本文主要介绍数字IC电源、时钟、接口相关的滤波设计。

1数字电源滤波

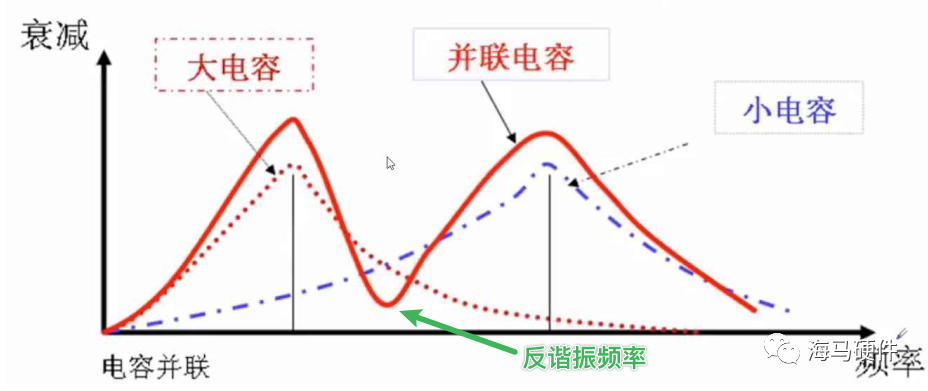

本文的数字电源特指给数字芯⽚供电的电源,通常把较高的电压降低到1.8V/3.3V等电压。数字电源往往电压⽐较低,并且电源引脚较多,因此⼀般使⽤电容滤波。电容滤波⼤/⼩容值配合使⽤,⼤电容储电(uF级别),⼩电容⾼频滤波,每个电源管脚⼀个,容值由滤波频率决定(⼀般⾼频取1nF、100pF,低频0.1uF)。 储能电容与高频电容配合使用,下图中间波⾕是反谐振点,由电路寄生电容&电感谐振导致,此频率附近的滤波效果最差,如果造成了影响,就需要考虑增加该频率附近的电容。

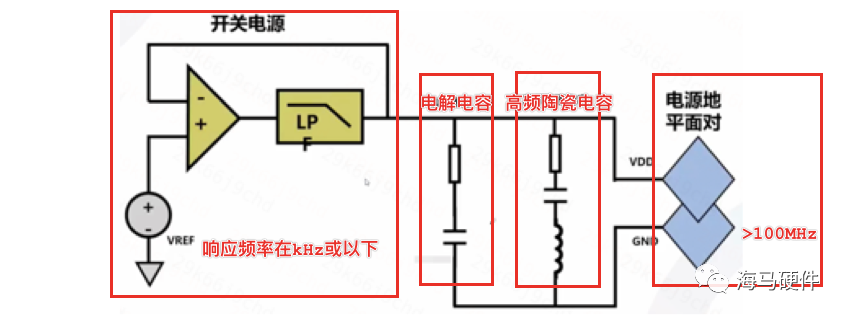

在数字系统中,电源分配系统(PDS,Power Distribution System)的质量直接影响着信号的质量。电源噪声表现为同步开关噪声(SSN)、地电弹噪声(GroundBounce)和回流噪声等,它直接影响着系统的噪声容限和信号的时序。 电源分配系统设计的关键是控制电源的目标阻抗。设计主要考虑的问题有:PCB 叠层方案、滤波电容的选择和放置、电源分割、连接器的选择等等。PCB 板上的电源分配系统由电源模块、电源地平面、各种电容组成。它们分别在不同的频率范围内作出响应:

电源模块响应的频率范围大约是从直流到kHz;

大的电解电容提供电流并在kHz 到 MHz的范围内保持较低阻抗;

高频陶瓷电容在MHz 到百 MHz的频率范围内保持较低阻抗;

PCB 板上的电源地平面对则在100MHz 以上发挥重要作用;

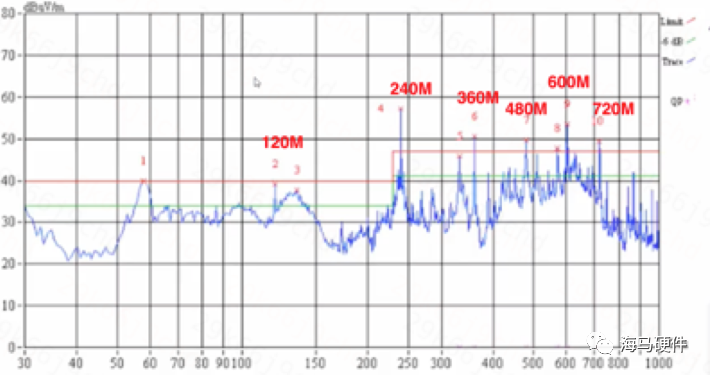

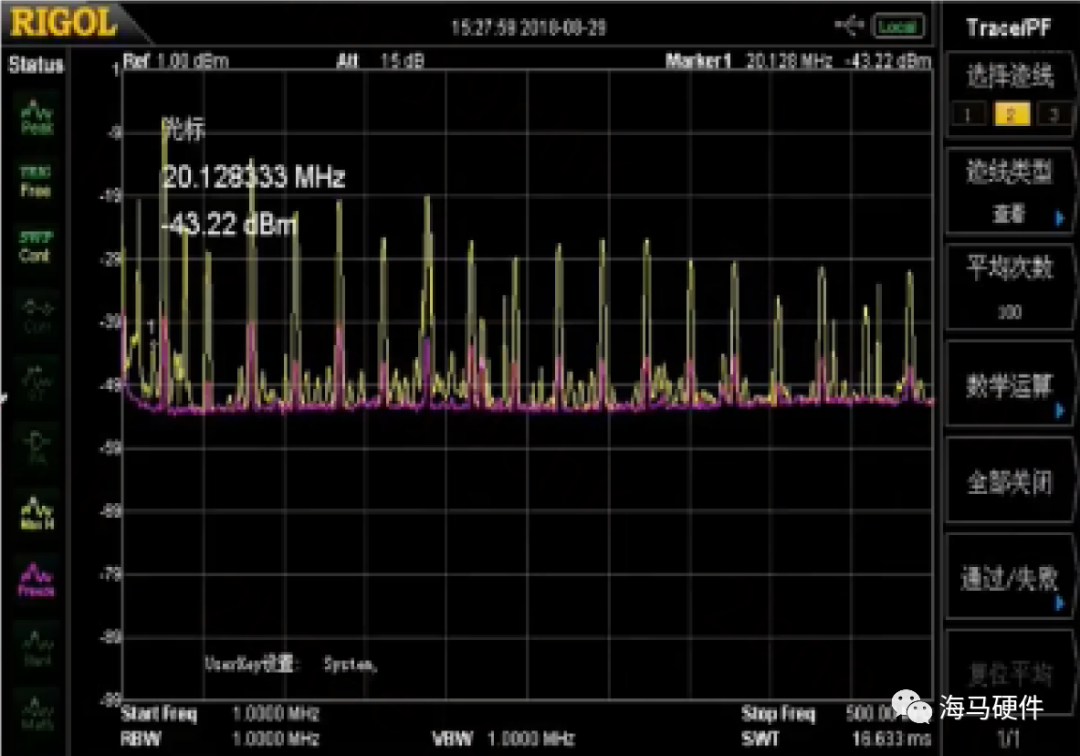

尺寸小的电容 (如 0603 封装)寄生电感较小,容值也小,因而其谐振频率较高,在高频情况下阻抗较低,常被用来减小 EMI 和回流噪声。尺寸较大的电容(如电解电容),可以提供比较大的电流,然而其谐振频率不高,这使得它的应用受到很多限制。 为了得到比较大的电容和较高的谐振频率,可以把几个小电容并联在一起 (N 个电容并联后,其容值为 NxC,电感为 L/N,谐振频率不变,ESR 减小为 R/N)。案例:SDRAM电源滤波不⾜,EMI测试不通过。 某产品进行欧洲 CE 认证,EN55022 空间辐射项目测试超标,导致产品不能认证上市。分析频谱发现主要是240、360、480、600、720MHz超标,超标频率是120M的倍频。

⼲扰源:数字电路时钟(SDRAM 120MHz)。

耦合路径:外接线缆(主要通过电源或地耦合)、PCB⾛线环路。

解决问题的主要思路是降低干扰源影响,同时在接口增加滤波电路,减弱耦合途径的效率。

接口处理:接口是主要耦合路径,因此信号端口需要进行滤波,主要是磁珠 +电容方式,磁珠选取 600R/100M,电容选择了 200PF。

原理图改进:SDRAM 时钟是干扰源,在匹配电阻后增加了对地滤波电容,取 10PF 左右(根据干扰频率决定)。同时增加电源管脚电容,容值取220pF。

PCB 改进:SDRAM 与 CPU 接口连接走线跨分割,地环路面积大,改进后的电容靠近电源引脚放置,IC下方地平面完整。

2 时钟滤波设计

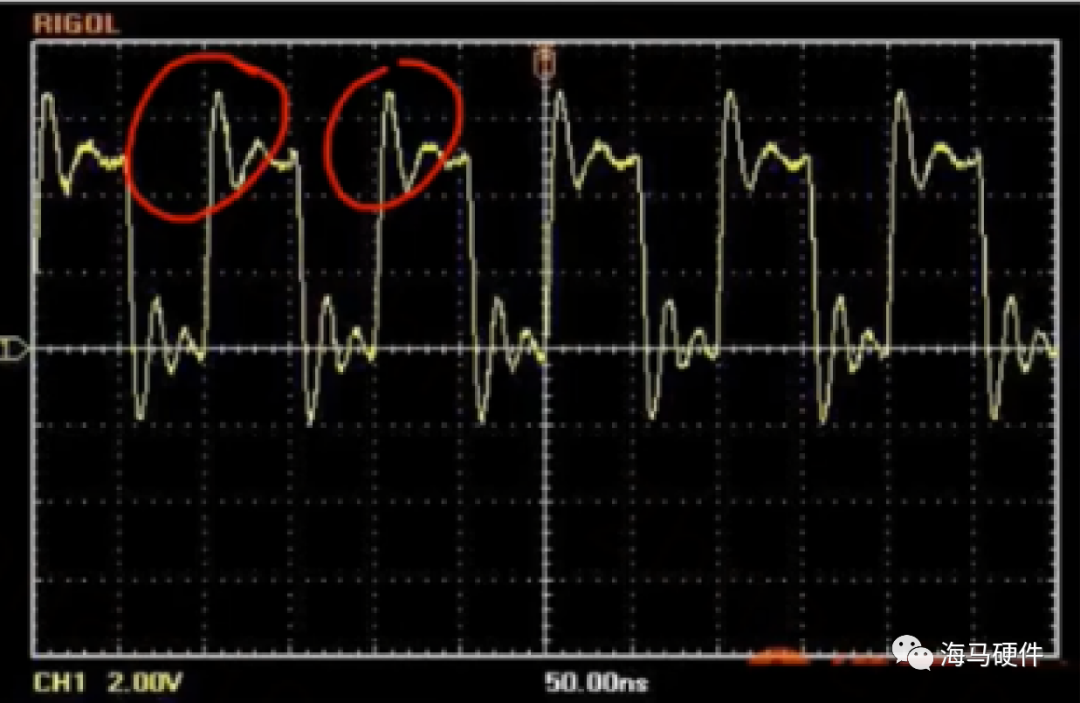

时钟信号也是干扰常见的源头之一,下图分别是时钟信号对时域和频域产⽣的影响:

周期信号的傅里叶级数展开式为:

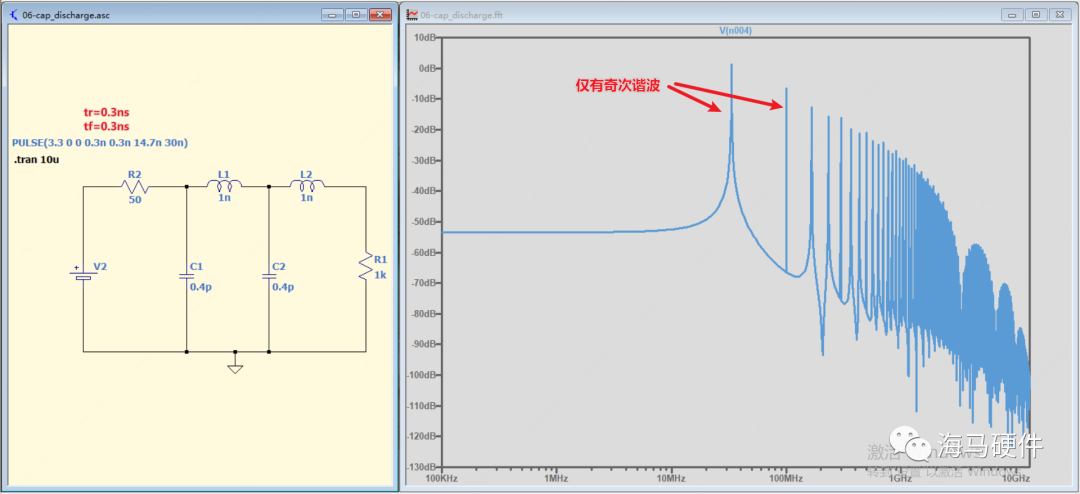

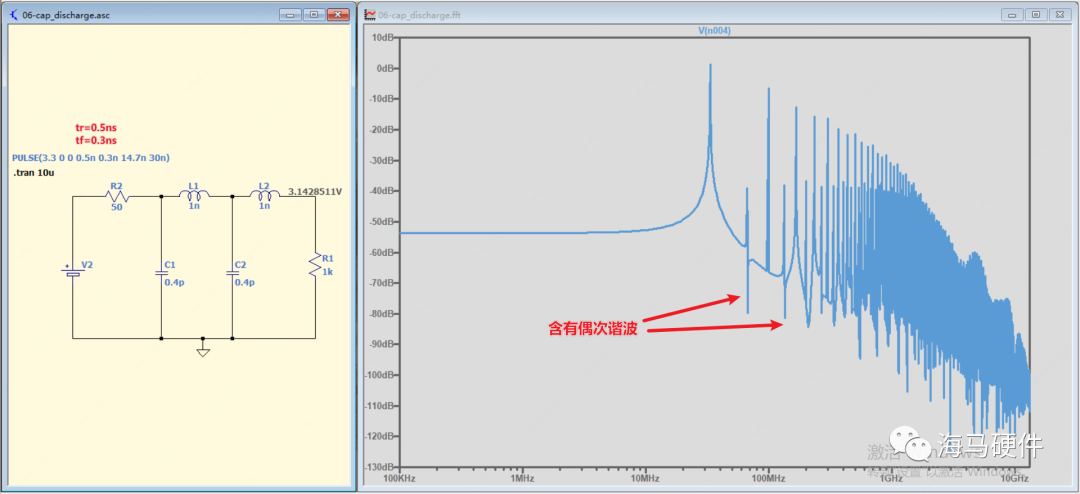

从公式中可以看到周期信号会有基频的奇次谐波分量(如1 3 5 ...),这是因为偶次谐波刚好被0相乘了。 但我们有时候也会看到偶次谐波,这往往是因为信号的上升/下降时间不一致,导致在频谱中看到偶次谐波,下图是利用LTspice完成的仿真对比,有兴趣的读者可以点开”电路原理图仿真工具2-LTspice仿真介绍“了解。

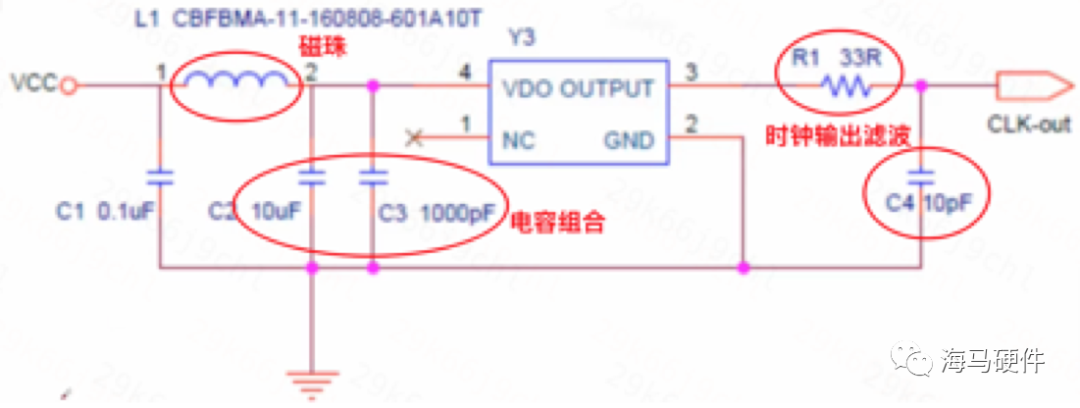

下图是有源晶振滤波电路的一个简单例子:

晶振的供电使用了磁珠+电容的组合,输出时钟增加了RC滤波。电阻通常采取 22R/33R/47R,有些低频时钟可以用磁珠替代。电容根据时钟频率选取,频率越高,电容值越小,一般100M 时钟选取 5pf 电容滤波,50M 时钟可以选取 22pf 电容滤波。 另外,建议设计时单板上 CLK 信号预留阻容滤波设计,最差情况是电容不焊接,电阻采取 0 欧姆替代。

3接口滤波设计

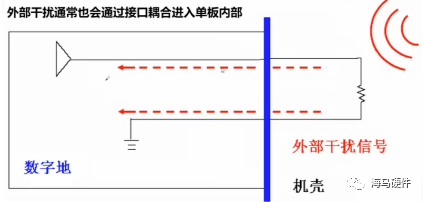

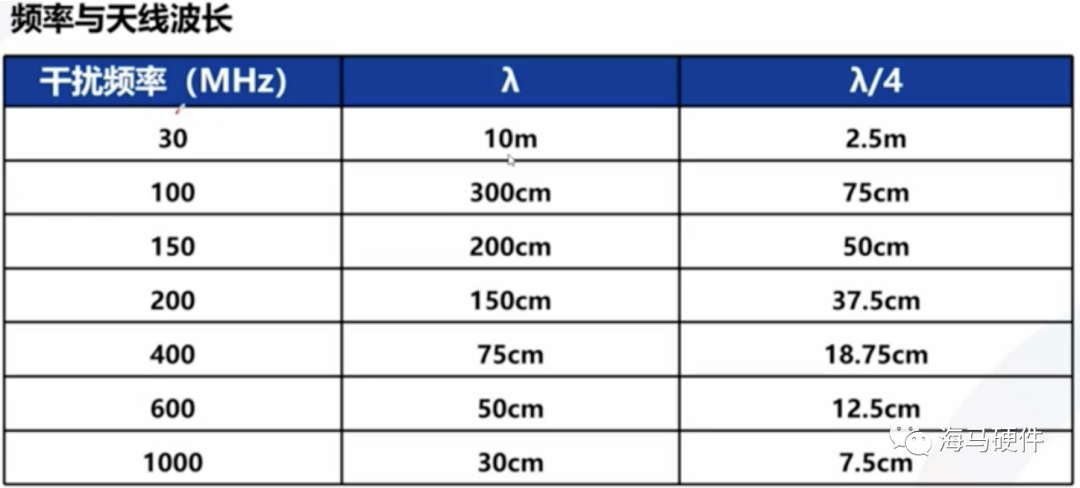

电子产品经常通过电缆对外通信,但电缆往往带来电磁兼容问题,主要原因是电缆可以传导电磁干扰,同时可以作为天线,接收和发射电磁干扰。 电子产品的电缆长度从几十厘米到几公里不等,可以在特定的频率进行发射与接收电磁干扰信号。当天线的长度接近无线电信号波长的 1/4 时,天线的发射和接收转换效率较高,受到的干扰也较大。频率和波长的关系(λ=c/f)如下:

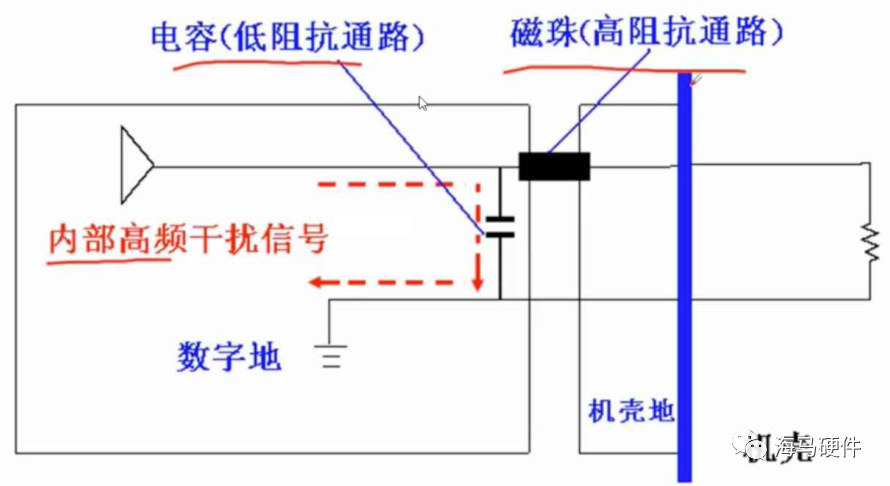

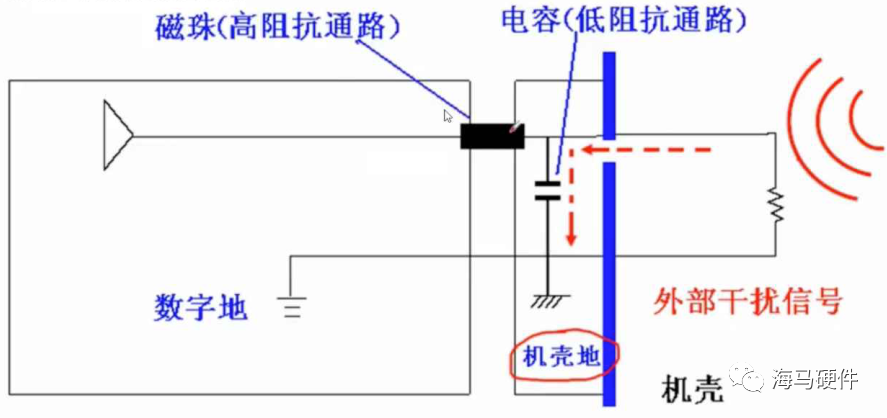

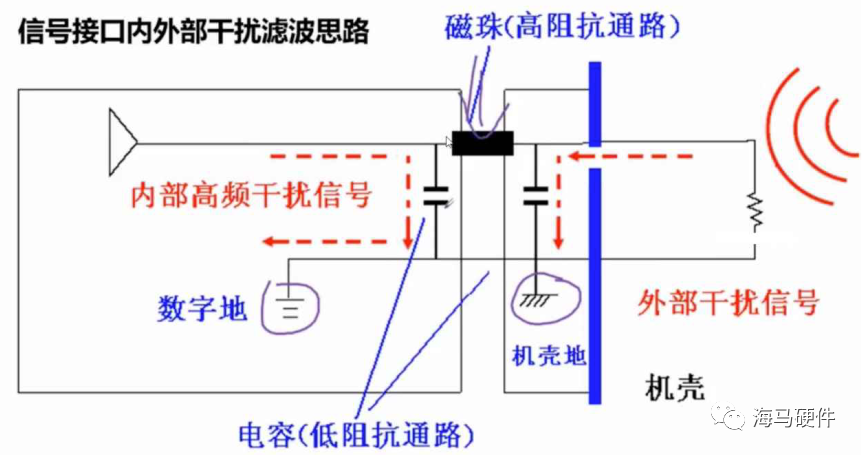

电缆干扰定位: 当遇到产品 RE 测试超标问题时,直接拔掉电缆的方式是最方便快捷的。如果发现确实是电缆导致超标,可以尝试在电缆上施加屏蔽接地等措施以外,另外在接口处采取滤波措施也是重要的手段。 1)针对内部干扰,通过电容等方式形成干扰信号的低阻抗通路,阻止其跑到外部。

2)针对外部干扰,一边是使用磁珠形成高阻抗通路,一边是将外部干扰通过机壳泄放到地,阻止其进入内部,右图是最完整的方案。

通信接口一般分为非差分接口和差分接口:

非差分接口通过公共地回流,比如232、PS2、VGA信号,通常使用电容+磁珠+电容的方式进行滤波(高速时使用串阻代替磁珠),通常不使用共模电感。

差分传输的特征是两根线束传输信号,两个信号振幅相同,相位相反,电流⽅向相反。典型的差分接⼝:485、CAN、HDMI、USB、LVDS、以太⽹等。通常采用共模电感滤波(例如USB、HDMI等都有专用的共模电感),中低速可以使用电容。

备注:

磁珠:确保对正常信号⼯作频率的阻抗<50R,滤波频率⼏⼗MHz〜1GHz,更⾼的频率就只能⽤电阻了,有些磁珠可以过⼤电流。

电感:滤波频率KHz〜100MHz,电感的额定电流通常会较⼤。

审核编辑:彭菁

上一篇:仿生设计助力高稳定性锌离子电池