时间:2023-04-23 15:20

人气:

作者:admin

常用电路模块的布局布线原则

常用存储器设计

*SDRAM

*FLASH

*DDR

*DDR2

*DDR3

*QDR

1、FLASH的设计

FLASH(闪速存储器)-速率较低

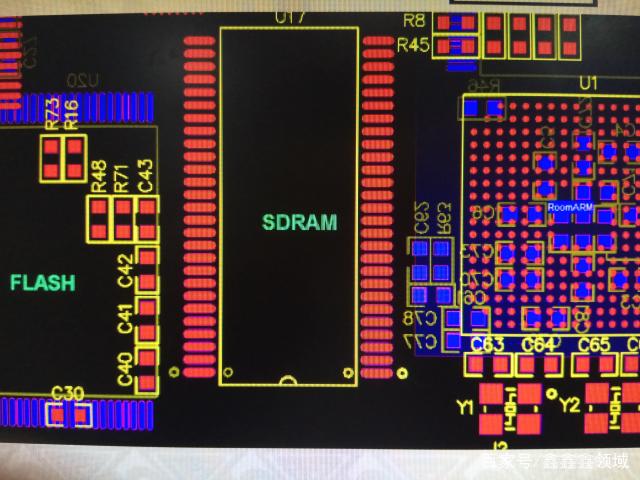

布局:一般采用菊花链

BGA->SDRAM->FLASH

(FLASH和SDRAM推荐距离为500~1000MIL),如下图:

2、FLASH的设计

布线(如图)

3W原则

等长范围:+-100MIL

特性阻抗:50欧

3、DDR的设计

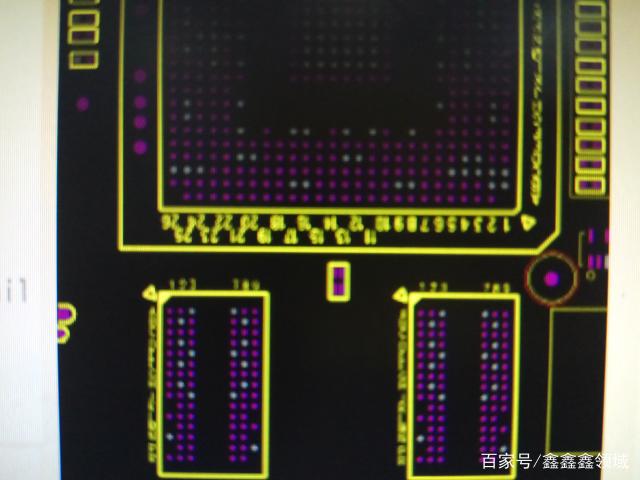

管脚定义解释(如下图)

4、DDR的布局

布局原则:靠近CPU摆放

DDR X1片时,采用点对点的布局方式,

DDR到CPU的推荐的中心距离:

当中间无排阻时:900~1000MIL;

当中间有排阻时:1000~1300MIL。

DDR X2片时,相对于CPU严格对称,如下图:

VREF电容的位置,如下图:

5、DDR的保护区域

DDR2保护区域(KEEPOUT REGION):DDR2内存组,所有同DDR相关的阻容电路,一直向CPU方向延伸至CPU的DDR控制器,称为DDR保护区域(DDR KEEPOUT REGION)。这个区域里需要满足一下条件:

A)不得出现与DDR无关的信号;

B)必须提供完整的地平面(信号线下方地平面不得中断);

C)必须提供完整的VCC_1V8电源平面(信号线下方电源平面不得中断)。

如下图:

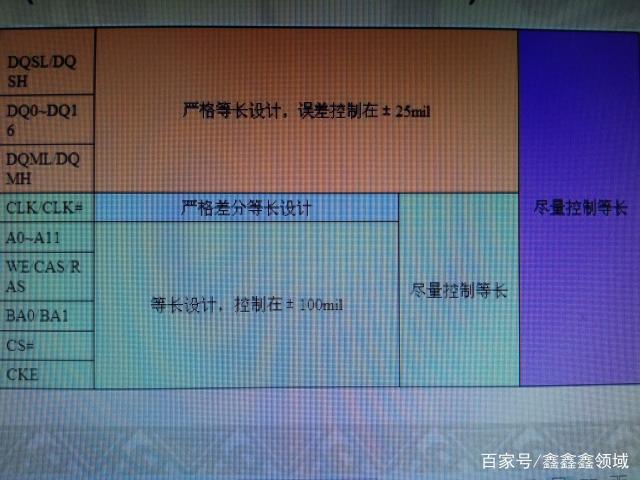

6、DDR的布线

特性阻抗:单端50欧,差分100欧;

数据线每10根尽量走在同一层;

信号线的间距满足3W原则

数据线、地址(控制)线、时钟线之间的距离保持20MIL以上或者至少3W

完整的参考平面

VREF电源走线推荐>=20~30mil

误差范围:

差分对误差严格控制在5MIL;

数据线误差范围控制在+/-25MIL;

地址线误差范围控制在+/-100MIL;

7、DDR的时序设计

DDR(采用树形或者星形拓扑)如下图:

下一篇:主电路和控制电路的工作原理