时间:2023-04-16 09:32

人气:

作者:admin

电力电子装置EMI滤波器平面集成研究

研究背景

随着宽禁带半导体功率器件的广泛使用,变换器正朝着高频率、高效率以及高功率密度方向发展。功率器件开关动作的高速化和高频化会导致系统电磁干扰问题恶化。电磁干扰与兼容(EMI/EMC)问题已成为限制变换器功率密度及可靠性的关键因素。EMI滤波器作为干扰抑制的重要手段,磁芯在滤波电感体积和重量中占据主要分量,多个分立电感的使用导致磁芯利用率降低,进而使得系统功率密度以及成本、体积并没有得到充分的优化,采用系统集成技术可以提高电感磁芯的利用率,从而进一步提高系统的功率密度。

成果简介

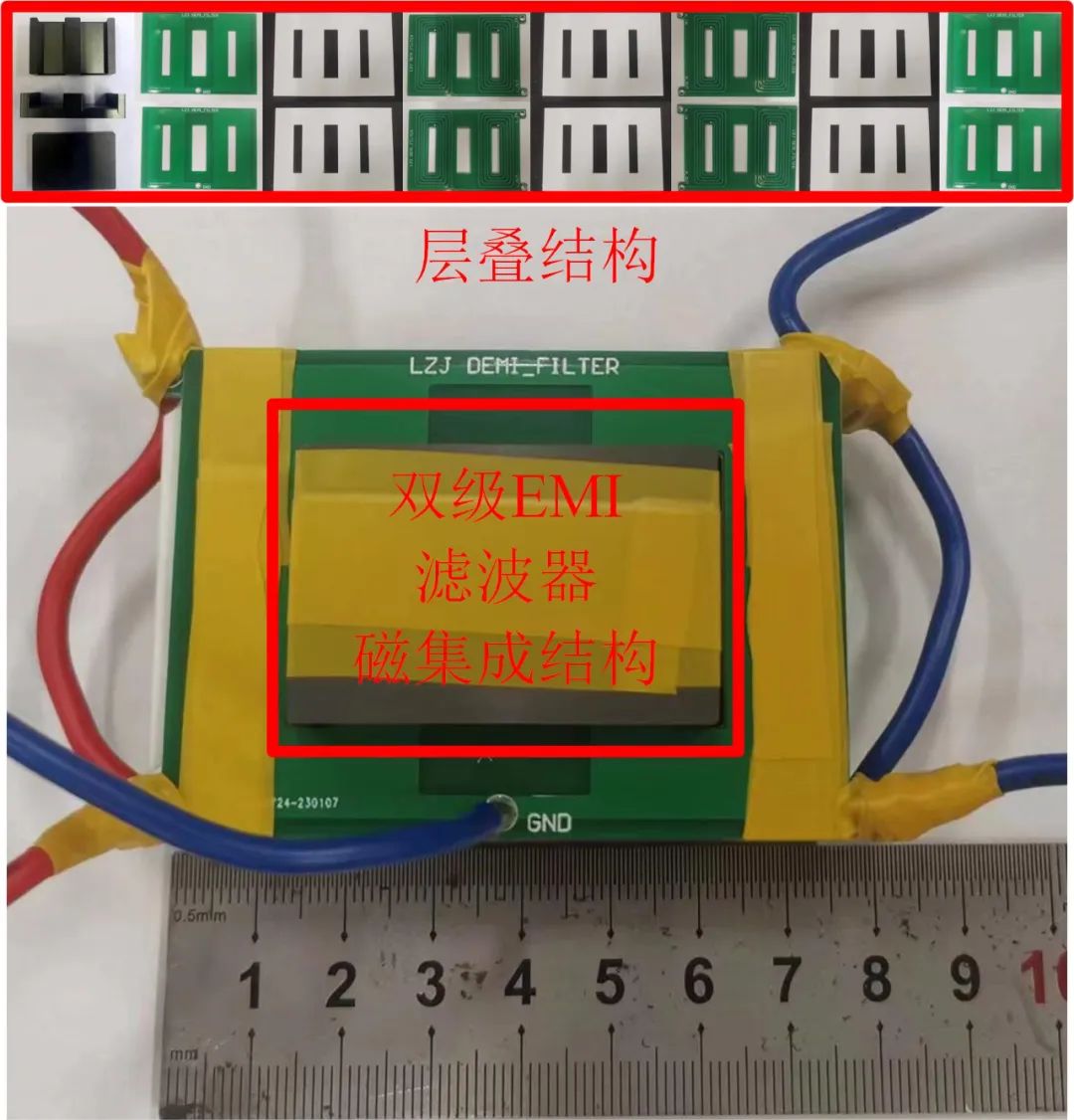

顺应逆变器高频化和集成化发展,针对开关频率提高所带来严重的电磁干扰问题,采用平面磁集成结构实现双级EMI滤波器。在EIE型磁芯上实现双级EMI滤波器所需电感绕组的磁集成,同时引入介电陶瓷实现电容集成。平面磁集成的双级EMI滤波器相比于分立元件的单级EMI滤波器具有更大的插入损耗,具备与分立元件双级EMI滤波器相同的噪声抑制效果,并且磁集成方案可以显著减小滤波器的体积和重量,提升系统的功率密度。

亮点提炼

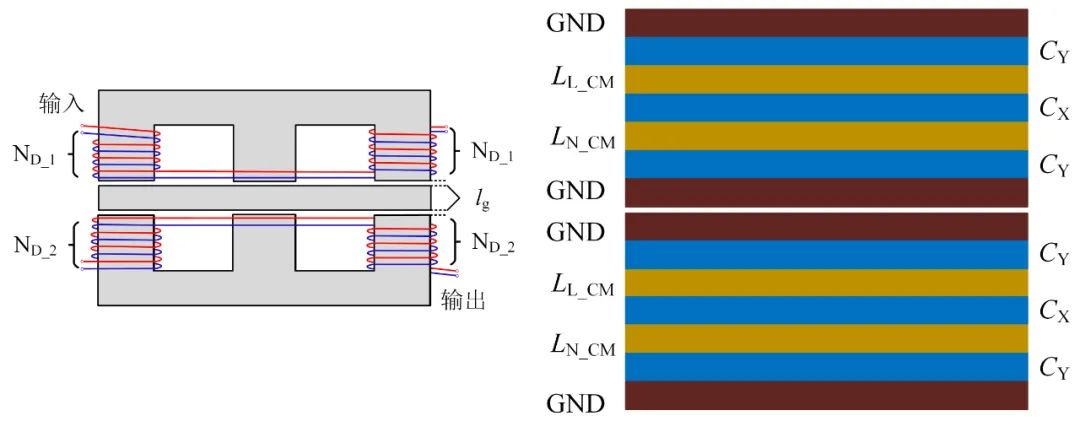

双级EMI滤波器的电感绕组,采用EIE型磁芯进行磁集成设计,绕组分布和绕制方向如下图所示。其中,E型磁芯的边柱绕制CM电感所需绕组,中柱提供CM电感的漏感通路,充当DM电感。E型磁芯和I型磁芯间均预留了合适的气隙,同时在中柱和I型磁芯的激励磁通方向相反,防止磁芯饱和,并有利于进行独立的磁路分析。根据绕组结构,在不同的平面线圈层间插入介电陶瓷片,进一步将双级EMI滤波器的滤波电容集成在一个磁芯单元,对应的层叠结构如图所示,可以有效减小平面线圈间寄生电容参数的影响。

图1 双级EMI滤波器绕组结构和层叠结构

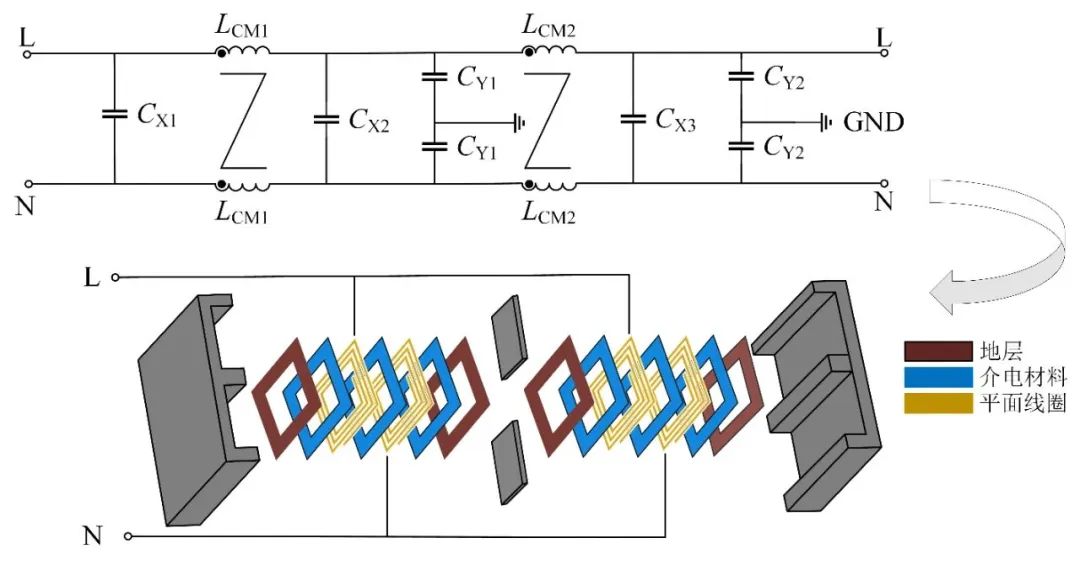

根据平面线圈的层叠设计,根据下图所示平面磁集成结构,通过平面线圈在磁芯上耦合形成CM电感,并利用结构中的漏感充当DM电感,不额外设置DM电感的平面线圈。同时在L线平面线圈、N线平面线圈和接地层之间加入介电材料,形成所需的CM电容和DM电容,实现了电感-电容的全元件平面磁集成结构。

图2 EMI滤波器平面磁集成结构

图2 EMI滤波器平面磁集成结构

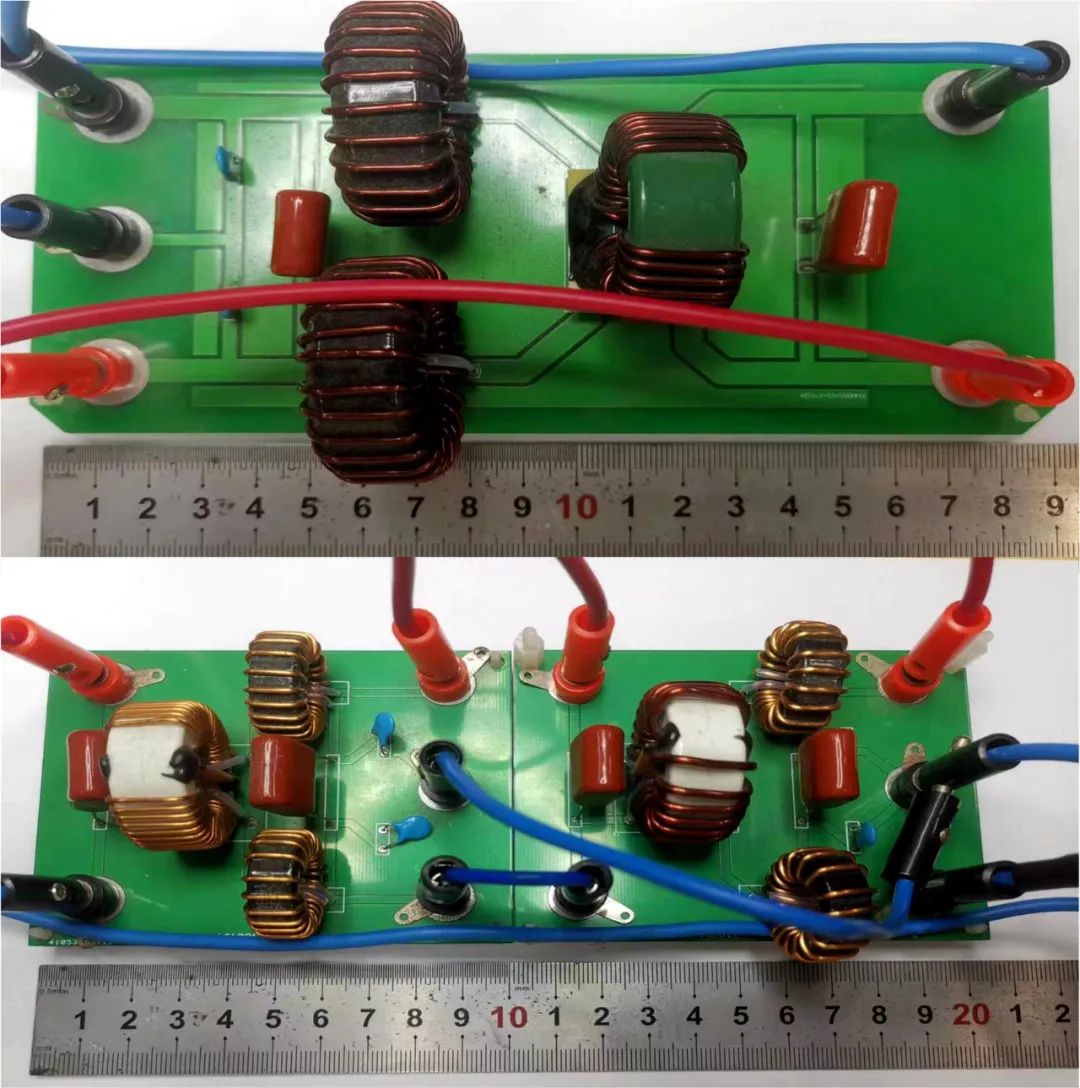

通过将平面磁集成结构与传统的分立元件的单级EMI滤波器和双级EMI滤波器进行对比,平面磁集成结构总体积相较于分立元件单级EMI滤波器减小了约46%,相比于分立元件双级EMI滤波器减小了约30%;重量上,则相较于二者分别降低了48%和34%。双级EMI滤波器具有更大的插入损耗,采用平面磁集成结构能够有效减少电感的重量体积,并能够进一步实现所需滤波电容的集成,能够提升系统功率密度。

图3分立EMI滤波器

图4平面磁集成双级EMI滤波器

前景与应用

本研究提出的EMI滤波器磁集成方案不仅为EMI滤波器的磁集成结构和参数设计提供了新思路和方案,也进一步提升了EMI滤波器的噪声抑制性能。相比传统分立型滤波器,所设计的磁集成EMI滤波器可以满足设计预期要求。同时,进一步减小了电力电子系统的体积和重量,提升了系统的功率密度。

审核编辑 :李倩

上一篇:开关电源模块的阻抗介绍

下一篇:如何降低电源噪声