时间:2023-02-06 09:30

人气:

作者:admin

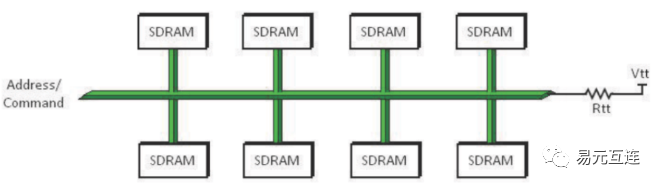

随着DDR频率的不断提高,DDR芯片也在不断增多,本文就以iMAX6的DDR设计来阐述。iMAX6采用4G(8片)DDR设计,使用CS[1:0]两个片选信号,每个片选信号各控制2G(4片)DDR,如下图所示,当使用这种拓扑结构时,终端的匹配电阻是不可缺少的。

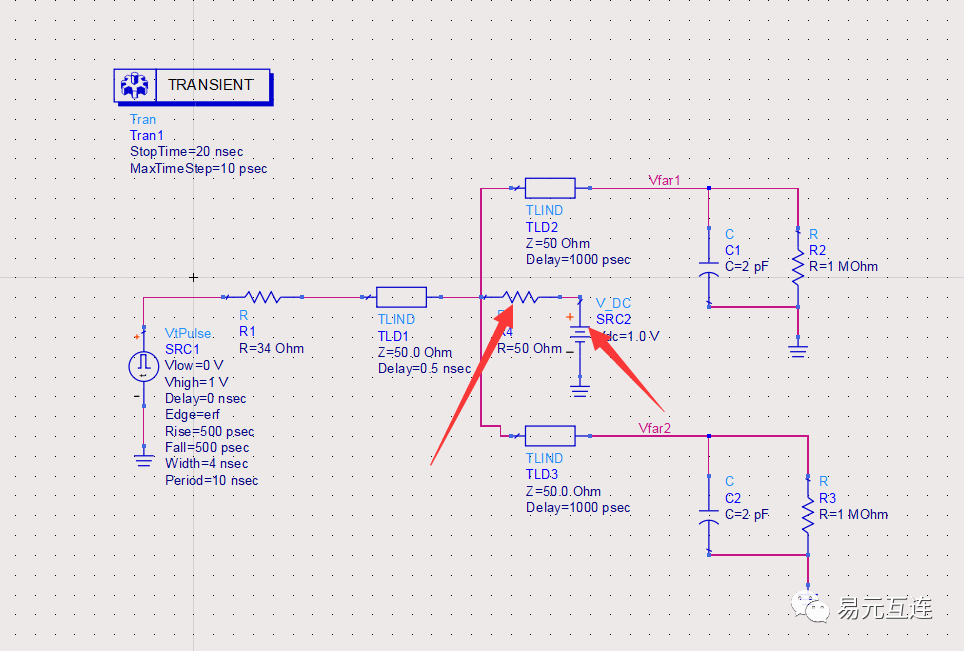

如上图,这个上拉的匹配电阻为什么要加?HW工程师也很难说清楚的,只是说是按照设计手册来添加的,今天小易就用ADS来仿真下添加匹配电阻和不添加匹配电阻的效果。 如下图先在ADS中新建一个信号完整性原理图,在DDR的分叉处添加一个50欧的上拉电阻。

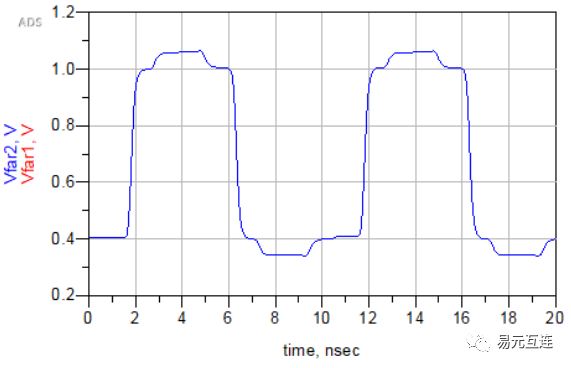

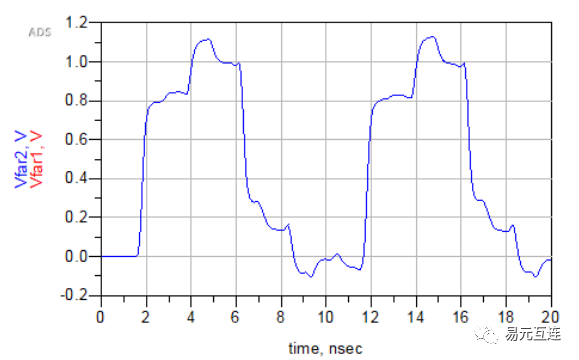

对该Address信号线进行仿真,仿真后的结果如下图所示。

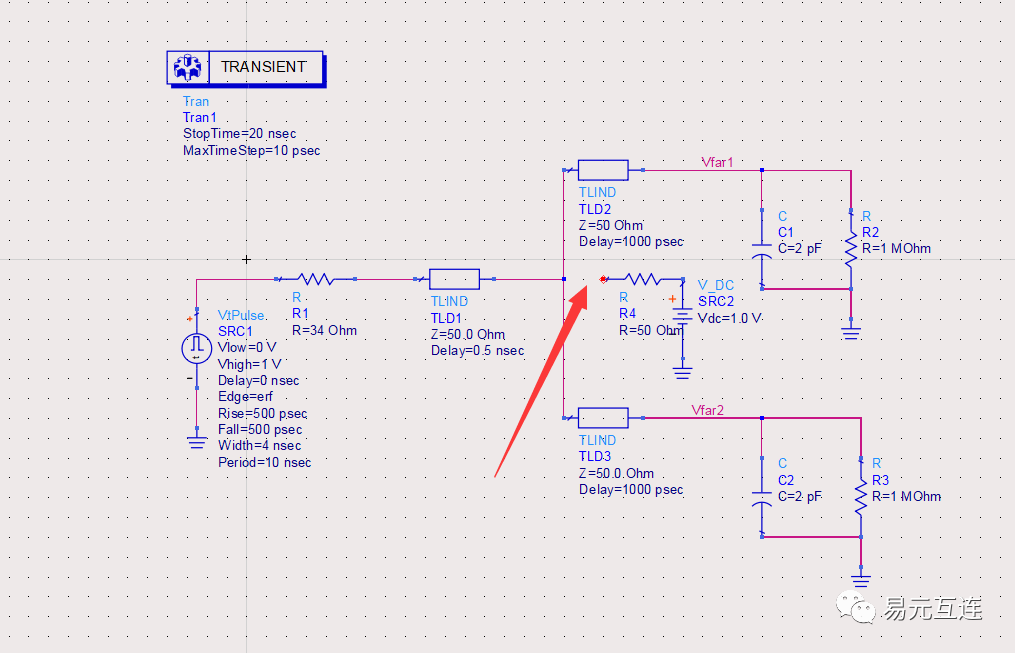

然后,将该电阻的电路断开,如下图所示。

然后,仿真后波形如下图所示,可以看到明显不如加了上拉的电阻的效果。

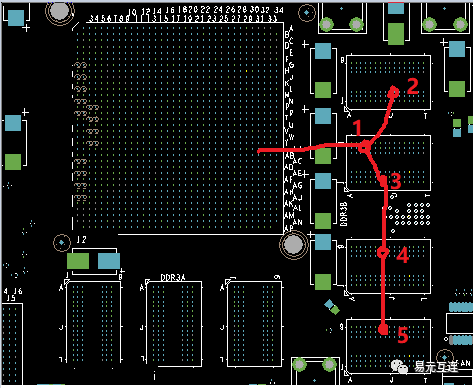

那接着讨论下一个问题,比如下图的布局,一根Address的线,要同时连接到4片DDR上去,1-5处打孔的地方都可以放置该上拉电阻,那究竟该放到哪处合适呢?

从ADS的信号完整性原理图上可以看到,仿真时将50欧的上拉电阻放在1的位置,也就是第一个从CPU打孔分叉的地方,这样效果才最好,放在其他地方的效果比较差,比如放在5处,实际和不放上拉电阻的效果差不多。

编辑:黄飞