时间:2023-06-28 15:40

人气:

作者:admin

概念

建立时间Tsu

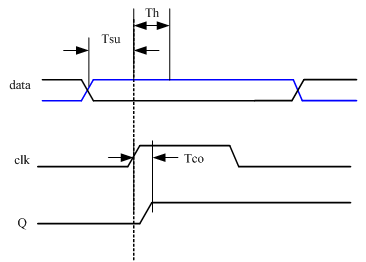

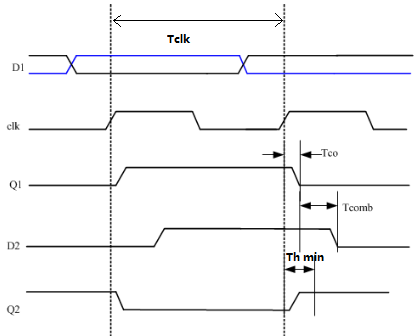

指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。对应图1的Tsu(Tsu:set up time)

图1. 触发器的波形图(参考“重要说明”里的触发器接口)

保持时间Th

在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。对应图1的Th(Th:hold time)

输出延时时间Tco

由 clk 触发到输出数据有效之间最大延 迟时间,对应图1的Tco(clock output delay)

触发器稳定判据

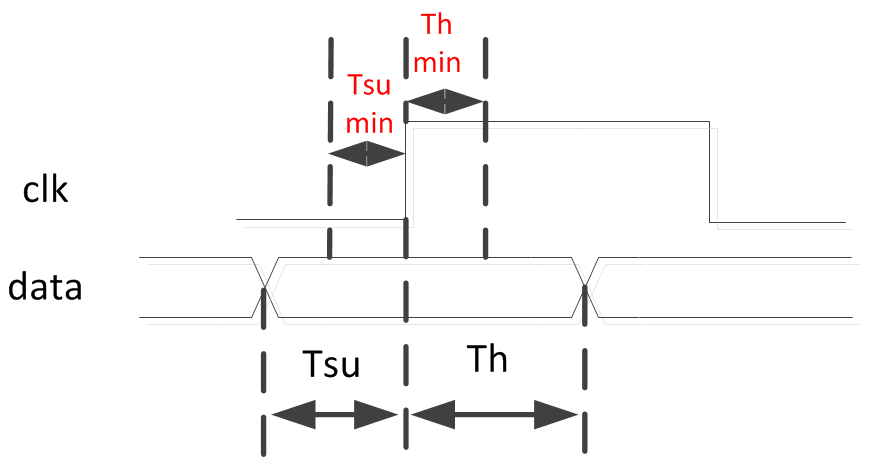

一个触发器是否不会产生竞争冒险,主要就看时钟和输入数据之间实际建立时间和保持时间是否大于触发器本身的最小建立时间和保持时间。参考图2,没错,稳定与否只和输入有关。红色字体是触发器的最小setup/hold时间,这个参数是器件本身的硬件特性决定的,我们改变不了。黑色字体是输入数据相对采样时钟的setup/hold时间,这个我们可以通过改变时钟与数据的相位关系去调整Tse和Th的大小。

图2. 触发器建立保持时间波形图

稳定判据

1.Tsu ≥ Tse min

2.Th ≥ Th min

3.以上两条同时满足,则触发器稳定,不会有竞争冒险

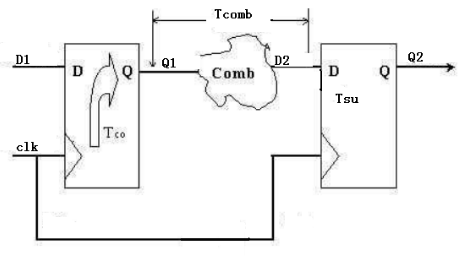

移位寄存器的原理

图3. 移位寄存器级联

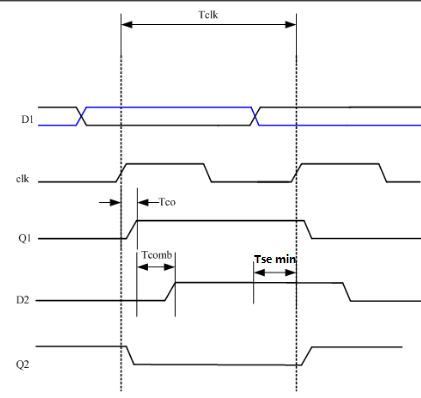

图4. 移位寄存器建立时间时序图

图4现象解释

参考图4,在第一个时钟上升沿,前边的触发器采集D1信号,将高电平打入触发器,经过Tco的触发器输出延时到达组合逻辑电路。又经过组合逻辑电路的延时Tcomb(我们假定组合逻辑电路此时没有改变信号的高低,可以把它假定为一个缓冲器)送到了D2接口上。

依据触发器稳定性判据可以得出,第二级触发器正常工作建立时间要满足以下边界条件:

实际建立时间Tsu = Tclk - Tco - Tcomb

Tsu > Tse min

图5. 移位寄存器保持时间时序图

图5现象解释

参考图5,在第二个时钟上升沿前边触发器采集到D1上的低电平,经过Tco的延时在Q1上得到表达。这个低电平在经过组合电路延时Tcomb到达D2。

依据触发器稳定性判据可以得出,第二级触发器正常工作保持时间要满足以下边界条件:

实际保持时间Th = Tco-min + Tcomb

所以Th > Th min

综上,同时满足Tclk - Tco - Tcomb > Tse min和Tco-min + Tcomb > Th min则第二级触发器稳定,如果触发器级联级数更多,那么以此类推。